# 第5章

CHAPTER 5

# 薄膜晶体管物理、性能 及其制造工艺

本章介绍半导体的表面物理、氢化非晶态硅(a-Si:H)TFT 的结构工艺和特性、多晶硅TFT 的工艺结构与特性,以及非晶态氧化物半导体TFTs 的结构工艺和特性。

无源 LCD 很难满足大容量信息显示的要求,因为大容量信息显示必然意味着扫描行数 N 很高,如最普通的 VGA 显示也要求分辨率为  $480\times640$ ,即扫描行数为 480。而当 N 高时会导致两个严重问题:

- (1) 驱动裕度随 N 上升而迅速下降。例如,当 N=300、400、500、600 行时,相应的 DM= 1.06、1.053、1.046、1.042,即显示态电压与未显示态电压之间的差别只有  $4\%\sim6\%$ 。这在工艺上、电源上以及液晶的温度特性上都是难以达到的。所以,目前 STN-LCD 的电光曲线 陡度虽然也能适应  $300\sim400$  行扫描线水平,但在实际应用中以 200 行为主,更高则采用分割矩阵法使分辨率加倍。

- (2) 当 N 上升时,占空比 1/N 下降,为了保证平均亮度必须提高驱动电压和采用高亮度的背光源(对于透射式 LCD)。这些措施对液晶器件的寿命都是不利的,何况有时即使采取了上述措施亮度也未必能达到要求。

无源矩阵驱动方式中扫描线数 N 受限制的一个重要原因是液晶像素电学特性的双向对称性,即加正驱动电压的效果与加负驱动电压的效果是一样的。如果在信号线和像素电极之间串接一个或若干个非线性元件,使复合像素具有非线性,消除原像素电学特性上的双向性,使每个像素可以独立驱动,从而克服交叉效应,实现多路视频画面。如果使复合像素还具有存储性,则还可解决占空比变小,亮度降低的问题。

在信号线与像素电极之间设置非线性元器件的矩阵驱动方式称为有源矩阵方式。有源矩阵的英文名为 active matrix,缩写成 AM。有源矩阵液晶显示器可缩写成 AM-LCD。根据非线性器件的种类可分为二端有源器件和三端有源器件两大类。

在 AM 驱动显示方式中,三端 AM 由于扫描输入与寻址输入可以分别优化处理,图像质量好,是主流,但工艺复杂,投资额度大。二端 AM 工艺相对简单,投资额度小,开口率大,但图像质量稍差,曾用于小画面显示器。由于现在非晶硅 TFT 工艺已非常成熟,已放弃二端 AM 使用。

在三端 AM 方式中目前均采用薄膜晶体管(thin film transistor, TFT)。TFT-AM 的主流是 a-Si(非晶硅)TFT。为了适应视频动态画面,还开发了多晶硅(P-Si)TFT。单晶硅(C-Si)AM-LCD主要用于液晶投影电视,其芯片尺寸一般小于 lin,这样就避免了单晶硅价格高的限制。

#### 5.1 薄膜晶体管的工作原理和结构

TFT 是有源矩阵的基础性器件,而 TFT 是半导体场效应器件,所以有必要介绍一些半 导体和场效应器件的基本知识。

#### 半导体表面物理 5.1.1

处理半导体表面物理时,关注的是金属-绝缘体-半导体(metal-insulator-semiconductor, MIS)系统的能带弯曲和表面电荷。这是金属栅极(gate,也称门极)上电压和半导体表面感 生电荷之间关系的基础,由此可引入平带电压(flat band voltage)和表面反转的阈值电压概念。

## 1. 理想的 MIS 电容器和能带弯曲

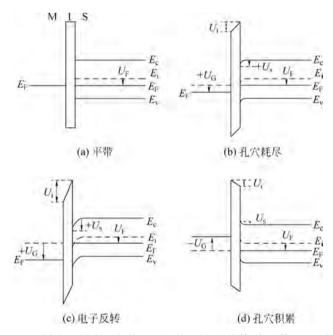

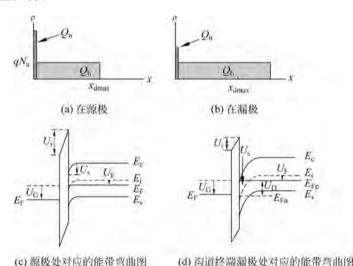

图 5.1.1 显示了一个在 p 型衬底上理想的 MIS 电容器的能带图。所谓理想,是指金属 和半导体的费米能级水平完全一致,这样不会在结构内诱导出能带弯曲,如图 5.1.1(a)所 示。实际上,由于金属和半导体之间功函数(work function,也称逸出功)的差异以及半导体 界面有界面陷阱态,情况要复杂得多。在下面的处理中,将约定:费米电位 U;是以体内的 本征能级  $E_i$  为参考点,在  $E_i$  下面是正的,在  $E_i$  上面是负的;同样,能带弯曲量  $U_i$  也是以 体内本征能级作为测量起点,极性习惯如同 $U_{F}$ 。

图 5.1.1 p型衬底不同表面电荷下理想的金属-绝缘体-半导体(MIS)的能带图

当一份正电荷 Q。放置在金属栅上时,它将在半导体中感应出一个相等相反的负电荷  $Q_{\bullet}(Q_{0}, \mathbf{n}, Q_{\bullet})$  都应理解为是单位面积上的电荷),负电荷将由半导体中电子密度的增加和自 由孔穴密度的减少组成,从而留下不动的负离子受主中心 N。。为了适应这些自由载流子密 度的变化,半导体内的能带在其表面附近向下弯曲,如图 5.1.1(b)所示。当对栅极施加一 个相对于半导体为正的偏压时,会出现如同在栅极上加正电荷的结果。按前面所讨论的约 定,给栅极施加正偏压 U<sub>G</sub>,金属的费米能级向下移动,半导体表面向下弯曲电位是+U<sub>s</sub>。 图中所示的情况是栅极上施加小的正电压,表面电子密度n、和N。相比是小的,称表面耗 尽(自由孔穴耗尽)。对于更大的正栅极偏压情况,如图 5.1.1(c)所示。在这种情况下,能 带的弯曲和 U,相应地增加,表面的自由电子密度大于 N,称现在这种情况为表面反转。 在这两种情况之间有一个能带弯曲的程度是 $U_s = U_F$ ,表面是本征的,即 $n_s = p_s = n_i$ 。进一 步增加正偏压,能带弯曲超越这一点将导致 $n_s > p_s$ 。最后,如图 5.1.1(d)所示,在栅极上施 加负偏压,自由空穴密度的增加,半导体内感应的正电荷增加。相应的能带向上弯曲一U。 称现在这种情况为表面积累。对于 n 型衬底,发生相反的情况。对栅极施加负偏压,逐渐增大 时,引起表面自由电子耗尽、反转,甚至空穴积累,以及正偏压将引起表面自由电子积累。

利用泊松方程和自由载流子密度对所处能级的指数依赖关系可推导出 U、Q、U。三者 之间的数学关系式为

$$Q_{s} = \pm \sqrt{4n_{i}q\varepsilon_{0}\varepsilon_{s}} \sqrt{\left[\frac{kT}{q}ch\frac{q(U_{F}-U_{s})}{kT} - \frac{kT}{q}ch\frac{qU_{F}}{kT} + U_{s}sh\frac{qU_{F}}{kT}\right]}$$

(5.1.1)

式中 ε<sub>0</sub>——自由空间的介电常数:

一半导体的介电常数;

k----玻尔兹曼常数;

g——电子电荷;

n:——半导体于本征态的自由载流子密度。

U。为正时,Q。取负值;U。为负时,Q。取正值。

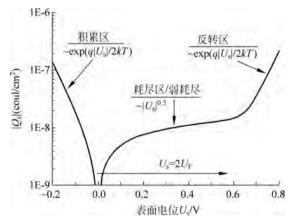

将方程(5.1.1)用于掺杂浓度为 $10^{15}$  受主/cm³ 的晶体硅衬底,得到 $U_s$  和 $Q_s$ 之间关系 的关键性特性,如图 5.1.2 所示。图中示出了前面讨论过的积累、耗尽和反转三个状态。在 积累和反转区,Q, 随 U, 成指数增加。在这两个区对 Q, 的主要贡献者是自由载流子,所以 在积累和反转区,相应地空穴和电子密度随 $U_s$ 成指数增加。在第三个区,即多数载流子耗 尽区,Q。随 $U_{\circ}^{0.5}$ 增加。将反转区曲线外推进入第三区可知,离化受主占Q。的主要部分。 因此,在这三区中不是自由载流子就是固定的空间电荷占Q,的主要部分。下面将会看到, 对于 TFT 材料这不是必须的,因为禁带隙中的陷阱态可以继续对 Q。做出主要贡献,即使 当表面有足够的自由载流子支持实质性的导电。

图 5.1.2 表面电荷随表面电位变化的计算值(衬底掺杂密度是 1×10<sup>15</sup> 受主/cm³)

由图 5.1.2 中的计算值可知, $qU_F$  比  $E_i$  低 0.288eV,在反转区中,从  $U_s$  >约  $2U_F$  开始 电子浓度主宰  $Q_{so}$  事实上,强反转区阈值的习惯定义是在  $U_{so} = 2U_{so}$ ,这时表面自由电子的 体积浓度  $n_s$  等于受主的体积浓度  $N_{so}$  当  $U_s = U_b$  时,表面是本征的 $(n_s = p_s = n_s)$ ,从能带 弯曲超出这点到强反转被称为弱反转( $p_s < n_s < N_s$ )。

在耗尽、反转区,能带弯曲U、是正的,因为U、和U。比kT/q大许多倍,方程(5.2.1) 简化为

$$Q_{s} \cong -\sqrt{2q\varepsilon_{0}\varepsilon_{s}} \left[ n_{i} \frac{kT}{q} \exp \frac{q(U_{s} - U_{F})}{kT} + N_{a}U_{s} \right]^{0.5}$$

(5.1.2)

方括号中的第一项与自由电子浓度有关,第二项与离化的受主空间电荷密度有关,它们与 U. 的关系是指数和开平方形式,分别与上面的相对应。这个简化表达式每项的物理意义明 显,是完整方程(5.1.1)很好的近似。

在平带和反转之间是耗尽区,离化的受主空间电荷成为主体,这时方程(5.1,2)可以进 一步简化为

$$Q_{\rm s} \cong -\sqrt{2q\varepsilon_0\varepsilon_{\rm s}N_{\rm a}U_{\rm s}} \equiv Q_{\rm b} \tag{5.1.3}$$

式中 Q。——半导体表面单位面积上耗尽深度内的离化受主空间电荷。

直观可以得出  $Q_b = -qN_a x_a(x_a)$  是能带弯曲程度为  $U_s$  时的耗尽层长度),将该式代入 式(5.1.3)可解得耗尽层长度

$$x_{\rm d} = \sqrt{\frac{2\varepsilon_0 \varepsilon_{\rm s} U_{\rm s}}{q N_{\rm a}}} \tag{5.1.4}$$

当 $U_s=2U_F$ 时,是从耗尽区变为反转区的转折点,这时 $x_d$ 最大,所以

$$x_{\text{dmax}} = \sqrt{\frac{2\varepsilon_0 \varepsilon_s 2U_F}{qN_a}}$$

(5.1.5)

方程(5.1.2)中的Q、可表达为Q、=Q<sub>0</sub>+Q<sub>0</sub>、式中Q<sub>0</sub> 是单位面积耗尽层中的电荷,Q<sub>0</sub> 是单 位面积反型层上的电荷。这些电荷处在深度为 U. 的抛物线位陷阱中,紧邻半导体表面。

## 2. 栅极偏置和阈值电压

施加在栅极上的电压,部分被绝缘层分压,设为 $U_i$ ,所以施加在半导体上的电压 $U_i$ =  $U_s + U_i$ 。若栅极上的电荷为 $Q_G$ ,半导体表面电荷为 $Q_s$ ,则 $Q_G = -Q_s$ 。 $U_i = -Q_s/C_i$ (单位 面积绝缘体电容),由此得到

$$U_{\rm G} = U_{\rm s} - Q_{\rm s}/C_{\rm i} \tag{5.1.6}$$

当 $U_s = 2U_F$ 时的 $U_G$ 是阈值电压 $U_{th}$ ,再利用式(5.1.3),由式(5.1.6)可得

$$U_{\rm th} = 2U_{\rm F} + \frac{\sqrt{2q\varepsilon_0\varepsilon_s N_a 2U_{\rm F}}}{C_{\rm i}}$$

(5.1.7)

当表面进入强反转区, $Q_n$ 成为 $Q_s$ 的主要部分时, $Q_n$ 的表达式为

$$Q_{\rm n} = C_{\rm i}(U_{\rm G} - U_{\rm th}) \tag{5.1.8}$$

由下面内容可以看到,式(5.1.8)广泛用于计算栅极电压大于 U1,时 MOSFET 的沟道 电流。同样的计算也广泛用于 TFT。由此可知,阈值电压 U,,是 ON 态 TFT 的关键参数。

与图 5.1.1 所示的理想 MIS 结构对照,实际的 MIS 结构可能会有栅极金属和半导体之 间的功函数差异,在氧化物中有固定的电荷以及在电介质/半导体界面有界面陷阱态。这些 都将改变零栅极偏压时的能带弯曲并影响 $U_{c}$ 和 $U_{s}$ 、 $Q_{s}$ 之间的关系。

#### 绝缘栅场效应晶体管 5.1.2

有源矩阵液晶显示器使用的 TFT 就是绝缘栅场效应晶体管(insulated gate field effect transistors, IGFETs), 本节讨论其基本工作原理和伏安特性。

## 1. 金属-氧化物-半导体场效应晶体管(metal-oxide-semiconductor field effect transistor, MOSFET)的工作原理

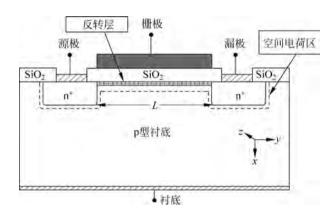

n 沟道 MOSFET 的示意图如图 5.1.3 所示。其中 n<sup>+</sup>掺杂的源区和漏区相距 L,L 决 定了沟道的长度。在这种特殊情况下,源区和漏区的边缘与栅极的边缘重合,这是标准的 MOSFET 的架构。称这种架构为自对准。以栅极作为模板,用离子注入对源区和漏区掺杂 实现自对准。沟道的宽度(沿垂直纸面的z方向)是W。垂直Si/SiO。界面的表面能带弯曲 是在 x 方向。栅电压大于阈值电压,显示表面的扩展区和耗尽层。

图 5.1.3 MOSFET 的截面示意图

在 ON 态时,源极接地,正偏压 Un 和 Ug 分别施加在漏极和栅极上。在 MOSFET 中 还存在着第四个端点,即 p型衬底的连接点,应该置于反向偏置,这会增加晶体管的阈值电 压。但在下面的讨论中认为它是接地的,这样设定不会对器件的特性有直接影响。对于 TFT,通常不用这个衬底的连接点。

要描述的器件模型是长/渐进沟道模型,在其中沿着沟道的电场(驱动 ON 态电流)远小 于确定反转层浓度的垂直电场,并且这两电场互不影响,因此基本上是二维现象,不会出现 短沟道效应。能带弯曲和能级的约定如同 5.1.1 节已规定的,即在半导体内所有的能量和 电位以本征电平作为测量原点,在本征电平以下的为正。

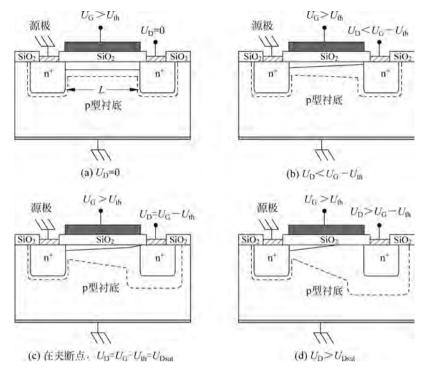

先讨论图 5.1.4(a)所示的情况。其中 $U_0$  大于阈值电压 $U_0$ ,沟道中出现栅极偏压感应 的反转层。如果漏极偏压是零,则沿着沟道的反转层将是均匀的。反转层中的电荷密度可 用反转的自由电子电荷密度  $Q_n$  和已离化的受主空间电荷密度  $Q_b$  表示,其中  $Q_a$  、 $Q_b$  和  $U_{th}$ 的关系为

$$Q_{\rm p} = C_{\rm i} (U_{\rm G} - U_{\rm th}) \tag{5.1.9a}$$

$$Q_{b} = qN_{a}x_{\text{dmax}} = \sqrt{(2q\varepsilon_{0}\varepsilon_{s}N_{a}2U_{F})}$$

(5.1.9b)

$$U_{th} = 2U_{F} + \sqrt{(2q\varepsilon_{0}\varepsilon_{s}N_{a}2U_{F})/C_{i}}$$

$$(5.1.9c)$$

图 5.1.4 不同漏极偏压  $U_D$  下, ON 态 MOSFET 的横截面(沟道被缩短, 栅极和 漏极偏压都是相对源极而言)

N。——衬底掺杂浓度;

$x_{dmax}$ ——反转区热平衡时表面耗尽层的最大宽度;

qU<sub>F</sub>——相对于半导体衬底本征电平的费米电平位置。

漏极为正偏压+U。时,n<sup>+</sup>漏极相对于 p 型衬底处于反向偏置,两者之间的电流限于结 的漏电流。在高质量结构中,这一点漏电流可以忽略不计。与此形成对照,漏极偏压引起源 极和漏极间反型层中电子漂移流。在沟道的漏极端,电子将掠过反向偏置的漏极空间电荷 区进入漏极结。

当漏极偏压 $U_{\rm D}$ , 低以及明显低于( $U_{\rm G}-U_{\rm H}$ )时, $U_{\rm D}$ , 将沿沟道的反型层均匀下降,导致在 源和漏接触之间沿沟道方向产生均匀场 $U_{\rm D}/L$ 和欧姆电子流 $I_{\rm d}$ 。由于这些地区是  ${\rm n}^+$ 掺杂, 可以假定在这些地区的电压降是微不足道的。定义这种情况下的器件工作于线性区。

增加 $U_{\rm D}$ ,沟道欧姆电流增加。最终 $U_{\rm D}$ 达到尽管仍小于( $U_{\rm G}-U_{\rm D}$ ),但已很接近( $U_{\rm G}-U_{\rm D}$ ) U,,)(如小于5%~10%)的某一值。这时,计算反转电荷密度需考虑沟道漏极端的电位。 例如,在沟道的漏极端,在反转层与栅极之间的氧化物上的电压降现在是 $U_G - U_{Ib} - U_{D}$ ,而 在沟道的源极端仍然是 $U_G - U_h$ 。因此,出现 $Q_n$ 沿着沟道逐步减少以维持电流的连续性, 并且随着 $U_{\mathrm{D}}$ 的增加,在漏极端的电压降较之在源极端的电压降增加更快,沿沟道的电场将 相应地发生再分布。现在,电流不再随 Un 线性增加,而变成亚线性,并且器件特性移出线 性区。这种情况如图 5.1.4(b)所示。此外,为了保持栅极上的电荷  $Q_0$  与半导体中电荷之 间的电中性,减少的 Q。被增加的 Q。平衡。这样,离化受主空间电荷层的厚度增加并超出 了热平衡值  $x_{dmax}$ ,见方程(5.1.9b)。 $x_{dmax}$  的值由下式给出

$$x_{\text{dmax}} = \sqrt{\frac{2\varepsilon_0 \varepsilon_s 2U_F}{qN_a}}$$

(5.1.10)

因此,耗尽层的宽度增加超过该值时,能带弯曲的量必须增加到超过 2U<sub>2</sub>,沿着沟道从源极 处的  $2U_{\rm F}$  逐步增加到漏极处的  $2U_{\rm F}+U_{\rm D}$ 。图 5.1.5 给出了在沟道的源极端和漏极端处电 荷分布和能带弯曲的变化情况。如图 5.1.5(d)所示,漏极的偏压造成非热平衡状态,使热 平衡的费米能级分裂成相距为  $qU_D$  的孔穴及电子的两个准费米能级  $E_{FD}$  和  $E_{FD}$ 。因此,此 图从物理上表明了为什么能带弯曲量 U、在漏极处必须增加到 2UF+UD: 是使表面的本征 能级比在漏极处的准电子费米能级低  $qU_{\rm F}$ 。这是反向偏置的  ${\bf n}^+$  栅极-p 型衬底二极管的  ${\bf p}$ 型表面反转的必要条件,是直接模拟在热平衡状态下情况,即当本征能级在热平衡费米能级 下面  $qU_{\mathbb{F}}$  时发生反转。

图 5.1.5 在  $U_D$  小于而又很接近( $U_G - U_{th}$ )的情况下沟道不同位置 的反转层电荷密度 Q。和耗尽层电荷密度 Q。

最后,如图 5.1.4(c)所示,当  $U_D = U_G - U_D$ ,在漏极处  $Q_B$ 减少到零,沟道被夹断。然 而,当到达漏极空间电荷区边缘的所有的电子扫过该边缘进入漏极时,这不是夹断电流, 而是电流达到饱和,使器件运行进入饱和区。称使器件发生电流饱和的电压为饱和电压  $U_{D(sat)}$ 。原则上,发生电流饱和的原因是最大可能的电位差  $U_{D(sat)}$ 已经降落在沟道上,即 使增加 $U_D$ ,夹断电压仍然维持在 $U_{D(sat)}$ 。然而,在现实中,当 $U_D$ 增加,漏极空间电荷区生 长,夹断点向源极移动。因此,即使沿沟道的总压降仍然是 $U_{D(sat)}$ ,但有效的沟道长度缩 短,这意味着平均电场增加。此情况如图 5.1.4(d)所示,电场增加导致相应的饱和电流增 加。因为夹断发生在  $U_{\rm D} = U_{\rm D\,(sat)} = U_{\rm G} - U_{\rm th}$ ,增加  $U_{\rm G}$  导致相应的  $U_{\rm D\,(sat)}$ 增加。由于  $U_{\rm D\,(sat)}$ 与 $U_G$ 相关联,这导致饱和电流随( $U_G - U_{th}$ )<sup>2</sup>增加。电流与电压的关系将在下面的部分详 细讨论。

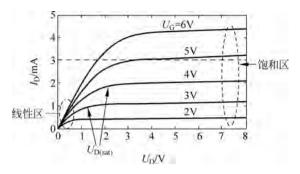

图 5.1.6 所示实验测得 MOSFET 输出特性说明了上面描述的几个关键特性,特别是 线性区和饱和区,随着 $U_G$ 增加,饱和电压值 $U_{\mathrm{D}(\mathrm{sat})}$ 也增加以及在饱和区有限的输出阻抗。

图 5.1.6 实验测得的 MOSFET 输出特性显示线性区、 饱和区以及有限的输出阻抗(W/L=25)

## 2. 简化形式的电流-电压方程

参照图 5.1.4(b) $\sim$ (d),沟道中任何点(x,y)的电流密度  $J_D$  为

$$J_{\mathrm{D}} = \sigma_{\mathrm{n}}(x, y) \, \mathcal{E}(y) \tag{5.1.11}$$

式中 ν——电流的流动方向;

x---垂直于 Si/SiO<sub>2</sub> 界面的方向;

$\sigma_{s}$ ——该点的电子电导率:

ℰ──沿电流流动方向的电场。

电导率 $\sigma_0$ 由下式给出:

$$\sigma_n(x, y) = q \mu_n n(x, y)$$

(5.1.12)

沿沟道的深度(从 Si/SiO<sub>2</sub> 界面到  $n=n_i$  之点  $x_i$ )和宽度 W 积分电子密度 n 得到处于 y位置的  $I_{\rm d}(y)$

$$I_{d}(y) = W \int_{0}^{x_{i}} \sigma(x, y) \ell(y) dx = -W \int_{0}^{x_{i}} q \mu_{n} n(x, y) \frac{dU(y)}{dy} dx$$

$$I_{d}(y) = -q \mu_{n} W \frac{dU(y)}{dy} \int_{0}^{x_{i}} n(x, y) dx$$

(5.1.13)

推导中假定电子迁移率与x和y方向的电场无关以及U(y)是沟道中y点的电位。反型层 中的电荷 Q。是体电子浓度沿沟道深度的积分,即

$$q \int_{0}^{x_{i}} n(x, y) dx = Q_{n}(y)$$

(5.1.14)

而 Q。与栅极偏压 U。有关,即

$$Q_{p}(y) = -C_{i} [U_{G} - U_{th} - U(y)]$$

(5.1.15)

将式(5.1.14)和式(5.1.15)代入式(5.1.13)中得到

$$I_{d} = -\mu_{n}W \frac{dU}{dy}Q_{n}(y) = \mu_{n}WC_{i} \frac{dU}{dy}[U_{G} - U_{th} - U(y)]$$

(5.1.16)

沿沟道从 0 到 L 积分 y 和从 0 到  $U_D$  积分 U(y):

$$\int_{0}^{L} I_{d} dy = \mu_{n} W C_{i} \int_{0}^{U_{D}} [U_{G} - U_{th} - U(y)] du$$

(5.1.17)

根据电流连续性原理, $I_a$ 与在沟道中的位置无关,因此有

$$I_{\rm d} = \frac{\mu_{\rm n} W C_{\rm i}}{L} [(U_{\rm G} - U_{\rm th}) U_{\rm D} - 0.5 U_{\rm D}^2]$$

(5. 1. 18)

这是经典的简化 MOSFET 方程,被广泛用于解释 TFT 的行为,特别是可用此式求出 载流子迁移率。

## 1) 线性区

对于 $U_D \ll U_G - U_H$ ,式(5.1.18)简化为

$$I_{d} = \frac{\mu_{n} W C_{i} (U_{G} - U_{th}) U_{D}}{L}$$

(5.1.19)

方程式(5.1.19)描述了线性区的电流-电压特性(电流随 Un 线性增加),并且从实验测得的  $I_{a}$ - $U_{c}$  传输特性的斜率求出电子迁移率

$$\mu_{\rm n} = \frac{L \, dI_{\rm d}}{W C_{\rm i} U_{\rm D} dU_{\rm G}} \tag{5.1.20}$$

称由式(5,1,20)得到的迁移率为场效应迁移率。

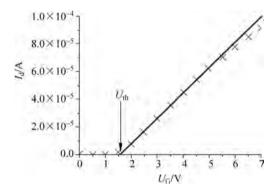

一个线性区的例子如图 5.1.7 所示。其中经过数据点有一条直线的斜率最大,由此求 出迁移率。将此直线外推到x轴上,交点给出阈值电压 $U_{th}$ 。广泛利用这个过程从TFT转 移特性得到这两个特征参数值。

图 5.1.7 实验测得的线性区转移特性的最适合直线

器件的跨导 g ... 为

$$g_{\mathrm{m}} \equiv \frac{\mathrm{d}I_{\mathrm{d}}}{\mathrm{d}U_{\mathrm{G}}} = \frac{\mu_{\mathrm{n}}WC_{\mathrm{i}}U_{\mathrm{D}}}{L} \tag{5.1.21}$$

沟道的电导度。为

$$g_{\rm d} \equiv \frac{{\rm d}I_{\rm d}}{{\rm d}U_{\rm D}} = \frac{\mu_{\rm n}WC_{\rm i}(U_{\rm G} - U_{\rm th})}{L}$$

(5.1.22)

## 2) 饱和区

当  $U_{\rm D}=U_{\rm G}-U_{\rm th}=U_{\rm D(sat)}$ 时,电流饱和成为  $I_{\rm D(sat)}$ ,方程式(5.2.29)简化为

$$I_{\text{d(sat)}} = \frac{\mu_{\text{n}} W C_{\text{i}} (U_{\text{G}} - U_{\text{th}})^{2}}{2L} \equiv \frac{\mu_{\text{n}} W C_{\text{i}} U_{\text{D(sat)}}^{2}}{2L}$$

(5.1.23)

因此,饱和区的电流随 $(U_{\rm G}-U_{\rm th})^2$  而增加,这是因为当沿沟道的电位降达到最大时,反型电 荷也是随 $(U_G - U_{th})^2$  而增加的。如同在线性区,从实测的饱和区的  $I_d$ - $U_G$  数据可以得到场 并利用方程(5.1.23)给出

$$\mu_{\rm n} = \frac{2L}{WC_{\rm i}} \left(\frac{\mathrm{d}\sqrt{I_{\rm d}}}{\mathrm{d}U_{\rm G}}\right)^2 \tag{5.1.24}$$

这是饱和区的载流子迁移率,也是场效应迁移率。如同在线性区那样,由计算迁移率的 直线与x轴的交点可给出阈值电压 $U_{tho}$ 。

饱和区的跨导为

$$g_{\text{m(sat)}} = \frac{\mu_{\text{n}} W C_{\text{i}} (U_{\text{G}} - U_{\text{th}})}{L}$$

(5.1.25)

## 3. 非理想的 MOSFET 特性

前面的讨论认为,阈值电压  $U_{th}$  仅仅决定于衬底掺杂浓度,这样,对于 n 沟道 TFT 的  $U_{th}$  是正的,对于 p 沟道 TFT 的  $U_{th}$  是负的。也就是说,两种沟道类型在零偏压情况下都是 OFF 态。称这种类型的晶体管为增强型器件。然而,实际的 MIS 结构将有下列几种(或全 部)情况:金属栅和半导体之间的功函数差 $U_{MS}$ 、介质中的固定电荷 $Q_{ief}$ 以及半导体/介质 界面的界面态  $N_{ss}(E)$ 中的电荷  $Q_{ss}(U_{s})$ 。这将产生一个非零平带电压  $U_{FB}$ 。在计算阈值电 压时需要考虑这个 $U_{EB}$ 。

如果  $U_{FB}$  足够负(例如,由于在介质中有大量正的固定电荷密度),那么,对于 n 沟道器 件,阈值电压将是负的,以及在零栅极偏压下,器件处于 ON 态。称这种器件为耗尽型器件。 仿之可知,耗尽型 p 沟道器件的阈值电压是正的。

由于功函数差和固定的氧化物电荷引起的阈值电压变化都将只是使 ON 态 MOSFET 的  $I_a$ - $U_a$  曲线沿栅电压轴移动,而不改变它的形状。此外,若只是固定电荷,对于 n 沟道和 p 沟道晶体管特性曲线的移动是相同的。然而,对于界面态,态中的占有电荷会改变能带的 弯曲量,所以当栅极偏压大于 $U_0$ 时,其对两种沟道线性 $I_0$ - $U_0$ 的影响都是减少其斜率,并 使它们互相远离。用式(5.1.20)分析指出,由于违反了这个方程关于当被高于 U,, 的栅极 电压感应的所有的电荷都是沟道中的自由电荷的基本假设,载流子迁移率将明显地减少。 当存在界面态时,被感应的电荷分成两部分:沟道中的自由电荷和界面态中处于费米能级 以上的陷阱中的载流子。

#### 氢化非晶态硅 TFT 的结构和工艺 5.2

氢化非晶硅(a-Si:H)TFT 主导着当前平板显示器行业,特别是对于有源矩阵液晶显示 器。本节介绍这些器件的结构和主要工艺。

a-Si:H 是 Si 和 10%氢的合金。氢在降低材料中缺陷起着关键作用,使悬挂键密度从 无氢 a-Si 的 1020 cm-3 减少到现在器件材料中的 1016 cm-3 。a-Si: H TFT 的性能特征决定 于材料本身的沉积条件,尤其是低温大面积等离子体增强化学汽相淀积(plasma enhanced chemical vapour deposition, PECVD)的条件。早期均匀 a-Si: H 的沉积面积只有约 10cm× 10cm,随后的工业发展导致现代商用 PECVD 反应器可以处理基板的面积超过 2m×2m。

# 5.2.1 a-Si:H 材料

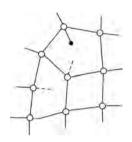

作为一种非晶态材料, a-Si 短程有序, 仍保持四配位, 但是键长和键角在材料容许的范 围内发生变化,所以不再长程有序。与晶体硅相比,键长和四面体键角分别是 0.235nm 和  $109.5^{\circ}$ ,在 a-Si:H 中这些值的均方根偏差分别约是 2%和 9%~10%。这种无序导致键能 量有一个分布并在材料内产生对缺陷结构有重要作用的弱键(weak bond, WB)。一般来 说, 硅原子是四配位, 配位缺陷发生在局部原子间的应变使弱键断裂。图 5.2.1 给出了一个 键的网络图,图中有两个悬挂键(dangling bond,DB)缺陷和一个已被氢填补的悬挂键。在 高质量的 a-Si: H中, 氢起着关键性的作用。由于氢的存在, 在弱键处形成 Si-H 键, 使弱键 密度降低到 10<sup>16</sup> cm<sup>-3</sup>。

图 5.2.1 包含悬挂键缺陷(虚线)和一个被氢填补的悬挂键(实心圆)的 四配位非晶硅的无序网络

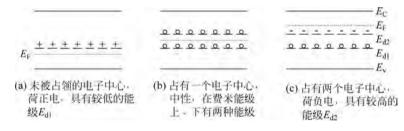

悬挂键态是两性的,它的中性态包含一个未配对电子,可以进一步捕捉一个电子变成荷 负电或释放未配对的电子变成荷正电。因此,这些缺陷有三个荷电状态:荷正电、中性或荷 负电(分别对应零、一个或两个电子)。对于 a-Si:H 悬挂键(包括单晶硅中许多深层次缺陷) 这类具有正相关能的缺陷,在禁带中双占有中心在单占有中心之上,而三种荷电态则是费米 能级位置的函数,如图 5.2.2 所示。当费米能级在较高电平之上时,缺陷荷负电;当费米能 级在较低电平之下时,缺陷荷正电;当费米能级在这两个电平之间时,缺陷是中性。此外, 只要在弱键中心至少已经有一个电子,不会存在双电子电平。未配位 Si 键具有一系列的与 载流子结合能,因此悬挂键在禁带中引起两种深能级中心分布。

图 5, 2, 2 两性悬挂键的电子占有和荷电状态是费米能级位置的函数

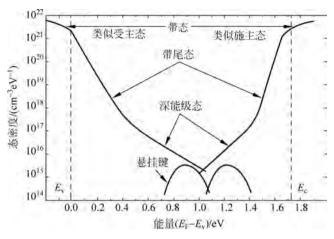

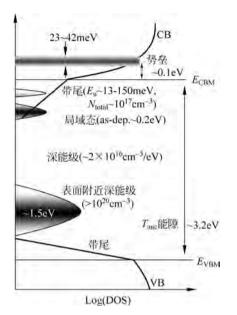

此外,缺乏在单晶 Si 中的长程的常规原子势导致生成局域和扩展电子态。在 a-Si: H 中局域态的特点是带尾态分布从导带和价带延伸进入禁带中。现在的禁带被称为迁移率带 隙,宽度是 1.85eV,它明显大于室温下单晶硅的带隙 1.12eV。对于低质量材料,在迁移率 带隙中存在高的缺陷密度,扩展态导电可以忽略不计,载流子传导是通过局域态陷阱之间的 跳跃。对于器件使用级的材料,导电是激发陷阱中的载流子进入扩展态,但是陷阱中的总电 荷只有一小部分能依靠热运动从陷阱中被释放出来,因此,测得 a-Si: H 的迁移率低。事实 上,由于高密度的带尾杰,已经不可能将费米能级提升到迁移率边以上,已观察不到纯扩占 态导电。a-Si: H 中的态密度分布如图 5.2.3 所示,说明了两个带尾态和由悬挂键态密度总 和决定的深能级态。

图 5, 2, 3 a-Si: H 的态密度分布

因此, a-Si: H中的主要缺陷是悬挂键和弱键态, 氢化建立的平衡发生在较大量的弱键 和较小密度的悬挂键以及已被氢化态之间。虽然,a-Si:H的沉积条件决定薄膜的弱键密 度,但在给定条件下,膜生长后,在氢、悬挂键和弱键之间的相互作用决定悬挂键的密度。材 料被定义为亚稳态,因为从膜生长温度冷却到500K时,缺陷结构被冻结(虽然准确的冻结 温度与冷却速率有关)。此外,在较低温度下经过足够长的时间,通过热激活弛豫过程将建 立一个新的缺陷密度平衡。激活能是 1.0~1.5eV, 与平衡时缺陷密度有关的激活能约是 0.2eV。平衡时材料内部的缺陷密度还与其他一些刺激,如掺杂水平的改变,光照引起的电 子-空穴对复合以及栅偏压引起的 TFT 沟道中自由载流子密度的变化有关。

#### a-Si:H TFT 的结构 5.2.2

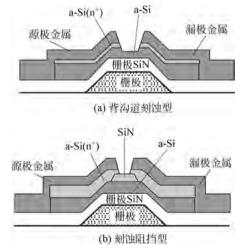

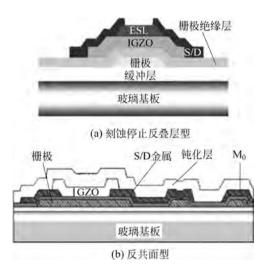

图 5.2.4(a)显示了最常见的 a-Si: H 结构。这是一个反向叠层型结构,由一个底金属

栅极、作为栅极介质层的非化学计量的氮化硅 a-SiN<sub>x</sub>:H以及在介质层上面的晶体管主体未掺杂 a-Si:H组成。与 TFT 的接触是 n<sup>+</sup> 掺杂 a-Si:H 的源极区和漏极区,它们的另一面与电阻较低的 金属斑点接触。称此结构"反向"是因为栅极在沟 道下面。所谓"叠层",是因为源极和漏极的接触 区与在 a-Si: H/a-SiN<sub>x</sub>: H 界面的电子沟道不共 面,前者与后者分别在 a-Si:H 薄膜的两面。因此, 沟道电流将需要流经 a-Si:H 层的厚度以完成源极 和漏极之间的电流连续性。同时,该结构基本上 是 IGFET(金属/绝缘体/半导体)结构,从表面上 看,与顶栅共面型的单晶硅 MOSFET 完全不同。 然而,在高产量和在大面积玻璃基板上低温处理 过程(分别为小于 350℃和大于 2m×2m)的限制

图 5.2.4 反向叠层型 a-Si: H TFT 的 结构的剖面图

下,从器件的性能来看,已经是为 a-Si: H TFT 开发的最佳结构。与在 p-n 沟道互补的 CMOS 电路中使用的 MOSFET 相比较还有另外两个主要差异。首先,因为 p 沟道器件的 性能较差,目前只有 n 沟道 a-Si: H TFT 有商业应用; 其次,源极区和漏极区相对于栅极边 不是自对准,需要加一个光刻对准阶段,在栅极与源、漏端部之间形成显著的寄生电容。后 者对AM-LCD 性能不利。

正如上面提到的,a-Si:H TFT 处理过程的一个关键方面是其高产量。部分是由于生 产过程中所需的光刻次数少(四次或更少),对于 AM-LCD,还额外需要一个掩膜板。相比 之下,制造一个复杂的单晶硅 CMOS 电路需要 12 次或更多的光刻阶段。

图 5.2.4 给出了两种稍微不同的 TFT 结构。不同之处在于图 5.2.4(b)中的 TFT 的 顶部有一层 a-SiN,:H。这两种结构有不同的制造步骤和行业标准,称图 5.2.4(a)中的结 构为背沟道刻蚀型(back channel etched, BCE)结构, 称图 5.2.4(b)中的结构为刻蚀阻挡型 (etch-stop, ES)结构。

由于 p 沟道 a-Si: H TFT 的场效应迁移率只有 n 沟道的 1%~2%,而其阈值电压又是 n 沟道的约 10 倍,所以 p 沟道 a-Si; H TFT 没有商业应用,只商业应用了 n 沟道 a-Si; H TFT。

#### 多晶硅 TFT 5.3

#### 5.3.1 简介

在公认 a-Si: H TFT 是大规模生产 AM-LCDs 最有前途的技术后不久,多晶硅(poly-Si, p-Si)作为替代的 TFT 材料出现了。低载流子迁移率(< 1cm²/Vs)的 a-Si:H TFTs 完全 适合对每个像素中的 TFT 寻址,但是不适合对显示器本身的行和列的快速寻址。近 20 年 以来,a-Si:H的载流子迁移率一直都在 $0.5 \sim 1.0 \text{cm}^2/\text{Vs}$ 范围内,相对应的,在同一期间多 晶硅的电子迁移率从小于  $5 \text{cm}^2/\text{Vs}$  增加到用常规过程可获得的约  $120 \text{cm}^2/\text{Vs}$ ,而采用能提 供类似单晶的大颗粒材料的创新技术,可高达约 900cm²/Vs。这样,可以将寻址电路以及 其他的电路集成在 AM-LCD 板上,导致诞生了第二代 AM-LCD 技术。但大规模生产的高 集成度的多晶硅显示器仅限于中小尺寸的便携式有源矩阵平板显示器,特别是对于较大尺 寸的笔记本、显示器和电视显示器,a-Si:H 仍是主流技术。因此,目前多晶硅主要应用在中 小尺寸的显示器,约占该领域中 AM-LCD 市场的 36%。此外,在小尺寸 AM-OLED 市场上 增长率几乎达 100%,尤其是智能手机。

#### 多晶硅的制备 5.3.2

正如上面提到的,在过去的 20 年左右,多晶硅的电子迁移率从小于 5cm²/Vs 增加到约 120cm<sup>2</sup>/Vs。这些增长是由于本节中将要介绍的材料制备技术的几个进化造成的。多晶 硅迁移率的上端已经可与低电场下长沟道 SOI(silicon on insulator) MOSFET 的值相 比拟。

在讨论多晶硅性能时,常用电子迁移率作为器件的品质因数。然而,应该注意到,在显 示器寻址领域中只有大迁移率是不够的,还必须同时有低漏电流和低阈值电压。此外,获得 这些参数的工艺过程需要能兼容玻璃基板,即理想情况下最大的处理温度保持低于约 450℃。即便是这种"温和"的温度也需要用比可在较低温处理的 a-Si: H 基板更硬的玻璃。 最后,由于整个工艺过程的复杂性,最终产品相对昂贵。

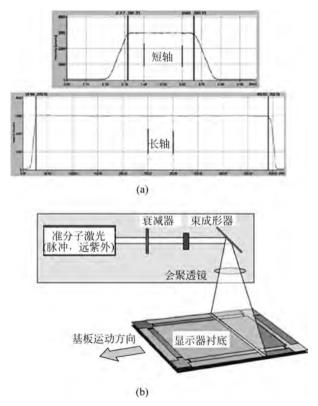

## 1. 准分子激光退火(晶化)(excimer laser annealing,ELA)

准分子激光(excimer laser)是远紫外气体激光,工作波长与所选择的气体混合物有关, 一般在 193~351nm 范围内。为晶化 a-Si,首选的气体混合物是波长为 308nm 的 XeCl,使 用波长为 248nm 的 KrF 准分子激光可得到类似的晶化结果,但是在工业化中,波长 308nm 的激光是首选,因为波长较长,对光路中的光学组件损害较少。这些都是脉冲激光器,其典 型的脉冲持续时间约是 30ns,最大的重复频率是 600Hz,可以提供高达 0.9J/脉冲的能量。 原始脉冲形状是半高斯型,尺寸约是 1cm×1cm。但是用于晶化,首选铅笔形的光束。在工 业生产中使用细长的线型束,其长轴方向的尺寸长达 465mm,而在短轴方向的尺寸下降到 350um。由于東外形在短轴方向陡峭的边缘,称此光束形状为"顶帽"束。除非另有指定,在 本节中提到的线型激光束都是这种形状。测量出工业用线型束的外形如图 5.3.1(a)所示, 准分子激光退火(ELA)晶化系统的示意图如图 5.3.1(b)所示,其关键部件由控制束强度的 衰减器、产生线型束的匀化器和束成形器以及将束聚焦到底层板上的聚光透镜组成。机械 驱动基板沿短轴方向匀速扫过激光束。

图 5.3.1 464mm×340mm 线型束准分子激光退火(ELA)系统的激光束强度外形与 ELA 系统原理说明

对于 248nm 和 308nm 波长的光, a-Si 膜光的吸收深度分别是 5.7nm 和 7.6nm,入射 能量在硅膜表面被强烈吸收,光照处的膜被强烈加热。如果入射能量密度足够高,能将该处 膜加热到熔点  $T_m(1420K)$ ,形成细晶粒膜。

用 ELA 处理的材料能够生产出电子迁移率为 250cm²/Vs 和 550cm²/Vs 的大颗粒高 质量的材料,但存在脉冲之间的稳定性和经营成本(频繁的充气、清洁窗口以及一般停机时 对激光管和系统的维护)问题。用掺钕钇铝石榴石(Nd:YAG)固体激光器的连续波(CW) 模式,可解决脉冲稳定和经营成本问题。

## 2. 金属诱导晶化

金属诱导晶化(metal induced crystallization, MIC)是一种金属参与提高 a-Si 变成多晶 硅晶化速率的固相晶化(SPC)过程。这种处理过程被视为是潜在的更简单、更便官和更均 匀的 ELA 替代品。同样,由于 SPC 过程加速了,就可以在较低温度和较短时间内完成晶 化,似乎这是一个更适于生产的替代传统的 SPC 的方法。然而,制成的 TFT 的 OFF 态漏 电流居高不下,限制了该技术的商业应用。

#### 栅极介质 5.3.3

如同在单晶硅器件中那样,多晶硅 TFT 首选 SiO<sub>2</sub> 作为栅极的介质层,相比之下, a-Si:H TFT 首选氮化硅。在 a-Si:H TFT 中首选 a-SiN:H 作为栅极的介质层是因为这 种材料的亚稳定性和氮化物中的正电荷能减少态密度的产生。对于多晶硅,不需利用材料 的亚稳定性,并且氮化物中的正电荷反而会引起阈值电压不必要的负向漂移,此外,氮化物 本身也容易受栅偏压的诱导造成陷阱捕获的不稳定。这些原因也是 MOSFET 器件不使用 Si<sub>3</sub>N<sub>4</sub>的缘故。

TFT 的栅极二氧化硅层的质量对器件的性能是至关重要的,需要氧化物具有低泄漏电 流、低的固定电荷密度和界面态、高击穿电场、低针孔密度以及好的偏压应力稳定性。此外, 对于与本书感兴趣的低温 TFT,氧化物沉积过程必须可以在玻璃软化点(450℃)以下实现, 最后,还要求大面积均匀性。温度限制排除热生长氧化物方法,而后者支撑了晶体硅集成电 路产业。

低温沉积 SiO<sub>2</sub> 的方法有以下几种:

- (1) 将氦气载体中的正硅酸四乙酯(tetraethylorthosilicate, TEOS)和 O2 混合气体用 PECVD 方法沉积,在 TEOS+He/O。流的比值中氧稀释率越高,膜越致密,孔隙度越低。

- (2) SiH<sub>4</sub>+O<sub>2</sub>,用常压化学气相沉积(atmospheric pressure CVD, APCVD)。

- (3) SiH<sub>4</sub>、O<sub>2</sub> 和 He,用遥控等离子,减压化学气相沉积(reduced pressure CVD, RPCVD),300 $\sim$ 350°C.

- (4) SiH<sub>4</sub>、O<sub>2</sub> 和 He,用电子回旋共振化学气相沉积(electron cyclotron resonance CVD, ECRCVD), 2. 45GHz, 25~270°C.

用这些方法制得的氧化物,经过检验都可以用作多晶硅 TFT 中的栅极氧化物。希望 沉积的温度在 250℃以上,对玻璃上的 TFT 不成问题,但是对低温聚合物基板上的 TFT 是 有问题的。然而,低沉积温度 ECR 的氧化物是高密度和低孔隙度的,可能用于聚合物基板 上多晶硅 TFT。

除了用作栅极的介电层,高质量的氧化物还用作隔离不同的金属化层(如栅极层和漏极 层)的层间介质以及覆盖玻璃基板的介质。覆盖层有两个功能: 在 TFT 的背界面提供一个 电子学上易控制的层和用作碱性离子扩散的阻挡层。

#### 名晶硅 TFT 的结构和制作过程 5.3.4

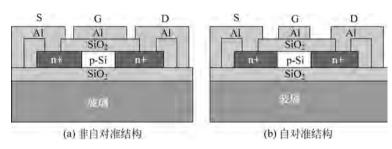

实现多晶硅 TFT 通常用如图 5.3.2(a)所示的非自对准(non-self-aligned, NSA)顶栅 结构和如图 5.3.2(b)所示的自对准(self-aligned,SA)顶栅结构。将会看到,这不同于 a-Si: H TFT 的反叠层结构,而与绝缘体上单晶硅(SOI) MOSFET 很相似。这样,多晶硅 TFT 可以用类似于 SOI MOSFET 的过程制造出来。例如,n 沟道和 p 沟道的 LTPS-TFT 的源 极和漏极的掺杂,可以分别用磷和硼的离子雨实现,即多晶硅 TFT 的结构和关键制造阶段 较之其他薄膜材料更接近 MOSFET。然而,这种高剂量离子掺杂过程对多晶硅膜的结晶程 度具有潜在的破坏性,较重的磷离子比硼离子的破坏性更大。损害的程度将取决于离子剂量、 离子能量和基板温度。已经表明,当足够高的剂量进入单晶硅,足以使注入层完全非晶化。

图 5.3.2 顶栅 n 沟道多晶硅 TFT 的横截面原理图

在图 5.3.2 中两种结构之间的本质区别在干源和漏极区的形成,这决定了栅极与这些 区域的重叠程度。对于有明显重叠的 NSA 结构,源和漏极区的离子掺杂在膜晶化之前,在 膜晶化过程中这些区域的掺杂剂将被激活。掺杂离子直接注入裸露的 a-Si 可以实现这个 过程,达到高水平的激活掺杂剂,而残余的离子损害最小。在 10 keV 下以  $1 \times 10^{15} \text{cm}^{-2}$  磷 剂量进行掺杂过程,通常给出掺杂区的薄膜电阻约为300Ω/□。这个阶段之后,沉积栅极介 质层并确定栅极形状,随后沉积栅极、源极和漏极的金属层并确定各个电极的形状。在栅极 金属与源和漏极掺杂区之间的重叠范围决定于光刻过程中对准精确度,可能约是 3 μm。这 是一个简单粗略的制造过程,适合对材料参数做基本研究,但结构有较大的寄生栅极-漏极 电容,将降低晶体管的高频性能。此外,由于对准问题,它不适合制造较短沟道器件(L <3µm),因为在激光晶化阶段,由于源和漏极区掺杂剂的横向扩散,有可能会造成沟道不受控 制的缩短。

采用 SA 结构可消除上面的限制,但是在源和漏极的掺杂阶段过程更复杂。

自对准的源极和漏极在掺杂阶段利用栅电极作为离子掺杂模板,达到栅极边缘与源和 漏极边缘之间的自对准,但这也意味着掺杂剂要通过栅极介质层才能注入。为了穿透这层, 使用的剂量和能量大于用于 NSA TFT 的。此外,因为掺杂过程在晶体管沟道层晶化之后, 为了激活掺杂剂必须引入一步处理过程:通过激光激活、在炉中热激活或快速热退火(rapid thermal annealing, RTA).

SA 掺杂过程引起的其他问题如下:

- (1) 制成的 TFT 的最小漏电流较大,这是由于在漏极结边缘有残余的离子掺杂损伤。

- (2) ON 态电流较低,这是由于在源和漏极区的薄膜电阻较大。

- (3)场效应迁移率较低,这是由于在栅极边缘处衍射诱导残余的损伤效应。

从上面的讨论中可以明显地看出,制造具有最小工艺性能缺陷的 SA TFT 的过程比制 造 NSA TFT 复杂得多,这是为什么在研究多晶硅材料的基本性能时首选 NSA TFT。然 而, SA TFT 潜在的优越性能, 如较低的寄生电容以及更好地兼容亚微米沟道长度 TFT, 成 为在许多多晶硅应用中的首选。

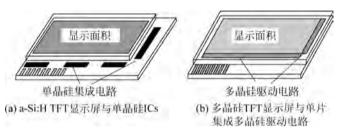

#### 多晶硅 TFT 的应用 5.3.5

采用逐行寻址的方法给 AM-LCD 的像素提供适当的信号,需要给显示器的行和列发送 适当的驱动信号。对于 a-Si: H 显示器,要完成这些功能, a-Si: H TFT 的切换速度太慢了, 因此必须在显示器的周边安装外部硅 ICs,如图 5.3.3(a)所示。这些电路可以直接附着在 板上,或通过安装了 ICs 的柔性的薄带连接。显示器的分辨率,即被寻址的行和列的数量决 定了这些 ICs 的数量。芯片的直接成本和安装成本将计入显示模块的成本。由于多晶硅较 高的载流子迁移率,可以将这些寻址电路直接印制在有源板上,如图 5.3.3(b)所示,由此降 低了模块成本。

图 5.3.3 带驱动电路的有源矩阵显示单元

因此,当前多晶硅 AM-LCD 主要应用是高容量的"移动"显示市场(移动/智能手机、数 码相机取景器、个人可携式多媒体播放器等),在这里电路集成提供了超越成本效益的诸多 优势。例如,这些便携式显示器需要坚固、重轻级和紧凑,多晶硅集成电路消除由于机械冲 击集成电路芯片脱离的风险。它们通过减少留给芯片键合的空间还减少了玻璃模块本身的 尺寸。最后,对于高分辨率、小对角线显示器,减少像素间距可能成为对准和压外部 ICs 的 限制因素,但用集成的驱动程序能更容易解决。对于 300ppi 以上的手机屏幕来说,LTPS TFT-LCD 技术是首选。

目前集成到多晶硅显示屏中的多晶硅 TFT CMOS 电路包括行和列移位寄存器、电平 位移电路、用于列驱动器的 6bit D/A 变换器、电荷泵和控制逻辑。

多晶硅 TFT 的其他新兴的应用是小型/中型对角线 AM-OLED 显示屏,尤其是智能手 机。目前,商业应用 AM-OLED 显示屏首选多晶硅像素 TFT,因为它可以提供 OLED 所需 的更高驱动电流。此外,这个应用需要高占空比 ON 态电流,在这些条件下,多晶硅 TFT 比 a-Si:H 有更好的偏压稳定性。

#### 非晶态氧化物半导体 TFT 5.4

非晶态氧化物半导体(amorphous oxide semiconductors, AOS) TFT 有如下几个独特 的特性:

- (1) 根据材料系统不同,具有 10~30cm²/Vs 的高电子迁移率,是 a-Si:H TFT 的几十倍。

- (2) 由于是非晶态,均匀性优于 LTPS。

- (3) 在低的温度下能够用传统的溅射工艺制作。

- (4) 通过后退火工艺可控制 AOS-TFT 的性能。

- (5) 光学透明。

- (6) 只有 n 沟道 TFT,由于在价带顶(VBM)上的高带尾杰和缺陷杰密度,不会发生反型。

- (7) 由于特性 4, 栅极绝缘体的材料选择范围大。

- (8) 沟道缩短到 50nm 都不出现短沟道效应。

对于对角线大于 90in, 帧频为 120Hz 的高分辨率 AM-LCD, 载流子的迁移率必须大于 2cm<sup>2</sup>/Vs, 这是 a-Si, H TFT 达不到的,而在面积上 LTPS 也做不到,只能用 AOS TFT: 由 干 AOS TFT 的迁移率高,更是大尺寸 TV-AMOLED 的首选 TFT 材料。

虽然 AOS 种类繁多,但目前进入大生产的只有 a-InGaZnO,下面的讨论也限于此。

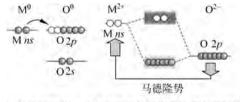

#### 5.4.1 AOS 的材料性质

AOS 材料的关键特性之一就是大的载流子迁移率,即使在非晶状态下也有晶态迁移率 的 50%或更多。这非常不同于 a-Si: H 与 c-Si 之间的差别,这种区别的关键在于 Si 的共价 键和 AOS 材料离子键之间的区别。杂化 sp³ 态形成 Si 的导带和价带,在非晶态 Si 网络中 有应力的和破碎的 Si-Si 键分别导致局域态和深能隙态。带尾态中的迁移率非常低,比晶态 中的减少 10 倍以上,这是因为在扩展杰中载流子的散射距离只有原子间隔量级。在 AOS 材料的离子键配置中,是由于金属阳离子和氧化物阴离子(如氧化锌)之间的电荷交换,金属 离子的外层 s 态是空的,氧离子的外层 p 态是满的。电荷交换生成使金属和氧离子轨道分 离的马德隆势(madelung potential),金属阳离子是空的 s 态主要形成导带最小值,负氧离 子的被充满的 p 态主要形成了价带最大值,如图 5.4.1(a)、(b)所示。对于原始的脉冲激光 沉积的 a-IGZO 材料,这些带边之间的间距约是 3eV,因此这些非晶态氧化物材料是光学透 明的。较新的溅射沉积的 a-IGZO 材料的 Tauc 光学间隙增加到3.7eV。对于金属氧化物, 金属离子的主量子数 n 决定了球对称的金属 s 态轨道的空间延伸。对于 n≥5 的如 Ga 和 Sn 这类后过渡金属,轨道的空间延伸足够大,相邻的阳离子之间有重叠,如图 5.4.1(c)所 示。这导致如在透明导电氧化物 ITO 中呈现小的电子有效质量和高的电子迁移率。显示在 图 5.4.1(c)中的晶格的 s 态重叠在无序的非晶态结构中仍保持着,如图 5.4.1(d)所示。因此, 在后过渡金属氧化物中延伸的 s 态轨道解释了透明 AOS 中相对较高的载流子迁移率。

(b) 在离子氧化物半导体中带隙的形成: (a) 电荷转移 显示载流子传导路径的导带底的分子 轨道形象

(c) 晶体氧化物半导体

(d) 非晶态氧化物半导体

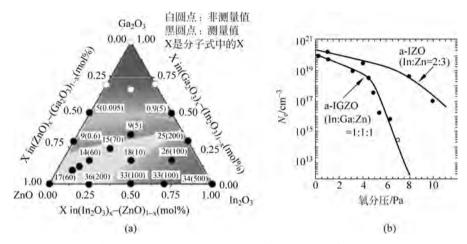

图 5.4.1 示意图

AOS 材料可以掺杂,由于离子键的适应性,通过引入不同价原子(对于 W 族半导体, 这 是标准做法) 达不到掺杂的目的, 但是可以通过最常发生的氧空位达到。产生浅施主能级的 未键合的金属阳离子造成这种空位。在沉积期间的氧分压决定空位浓度,对于低分压,三元 结构 In。O。-Ga。O。-ZnO 的组分和霍尔迁移率之间的关系如图 5.4.2(a)所示。在这个材料 组成空间中,大部分是非晶态的,只有纯度高于90%的ZnO或In。O。是晶体的。然而,沿三 角形的底边可看到,组成的差异对迁移率的影响甚小,而增加 Ga 含量会减少迁移率和自由 载流子密度。在 TFT 材料中,为了确保低的 OFF 态电流,需要低的自由载流子密度,Ga 在 这方面起重要的作用,因为强大的 Ga-O 键降低了氧空位。此外,在沉积过程中增加氧气分 压可以进一步降低自由载流子浓度,如图 5.4.2(b)所示。同图中比较了 a-IGZO 和 IZO,也 显示了在这些材料中掺入 Ga 的重要性。出于这个原因,对于 TFT,InGaZnO,(IGZO)是首 选的组分,即使它的迁移率不是最高的。

图 5.4.2 三元结构 In<sub>2</sub>O<sub>2</sub>-Ga<sub>2</sub>O<sub>2</sub>-ZnO 的组分和霍尔效应迁移率和自由载流子密度(括 号中单位是 10<sup>18</sup> cm<sup>-3</sup>)之间的关系以及在沉积 a-IGZO 和 a-IZO 膜过程中,自 由载流子密度与 O<sub>2</sub> 分压之间的关系

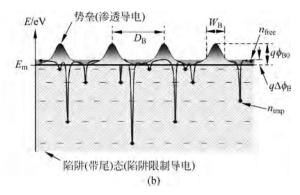

霍尔迁移率随载流子密度增加而增加,归因于受导带内周围势垒限制的渗流。图 5.4.3 给出了 a-IGZO 态密度(DOS)的图解说明,包括渗流势垒(以它们的平均高度表示)、E conter 和 ΔE 分布。浅施主能级和导带边的低密度带尾位置也显示在此图中。p 型态组成价带 边,但没有像导带态那样重叠的轨道,所以加在带迁移率边上形成高密度的局域态和深能级 态,使p沟道TFT的性能很差。

# AOS TFT 的结构与制造

不像 a-Si: H 和 LTPS TFT 那样, AOS TFT 技术仍在发展中, 没有一个确定的达成共 识的良好的制造技术过程。然而,已有一些新兴趋势用于制造高质量显示器的 TFT 结构 和流程。

## 1. 结构

a-IGZO TFT 目前首选叠层或共面底栅结构,如图 5.4.4 所示。广泛应用反叠层结构, 但主要是图 5.7.4(a) 所示的刻蚀停止型。在 5.3.2 节中描述过两种主要的倒叠栅 TFT 结构:

图 5.4.3 a-IGZO 态密度(DOS)分布示意(显示 带边、带能隙和导带中渗透电位分布)

图 5, 4, 4 a-IGZO TFT 结构横截面

背沟道刻蚀(BCE)型和刻蚀阻挡(ES)型,对于a-Si:H TFT,BCE 更适合大规模生产。然 而,对于 a-IGZO TFT,因为背沟道对环境效应敏感,对在沉积和刻蚀源和漏金属过程中的 损伤和施主形成也敏感,所以 ES 结构是首选。直接比较 BCE 和 ES TFT 的性能证明了这 一点: ES TFT 有用 PECVD 方法沉积的 SiO, 刻蚀停止层,两种器件的源和漏金属是通过 溅射和干式刻蚀得到的 MoW 层,栅极介质层是用 PECVD 方法沉积的 200nm 厚的 SiN,, BCE 和 ES TFT 的电子迁移率分别是 5.0cm²/Vs 和 35.8cm²/Vs。因此,由于在 BCE TFT 中不受保护的 a-IGZO 膜背面遭到损伤,导致器件性能退化接近一个数量级。

### 2. 制造过程

## 1) a-IGZO 层

FPD TFT 中的活性 a-IGZO 层的典型厚度是 30~60nm,通常是在室温下由直流溅射 沉积。溅射靶的成分是  $In_2O_3$ :  $Ga_2O_3$ :  $ZnO_4$ 其比率在  $1:1:0.5\sim1:1:1$  范围内,溅射 气体是 Ar/O。混合气。也使用包括脉冲激光沉积和射频溅射沉积的其他技术,直流磁控溅 射的优点是已被广泛用于 AM-LCD 中的铟锡氧化物(ITO)沉积,并且其大面积沉积的设备 是现成的。

## 2) 栅极电介质

在显示器中,栅极电介质层厚 200nm,大多数是用 PECVD 方法沉积的 SiO,,然而,在 某些情况下也使用用 PECVD 方法沉积的 SiNx 和 SiOx Nv。

## 3) 沉积后退火

a-IGZO TFT 结构常用沉积后退火,已证明该过程可使器件的性能和一致性发生重大 的改进。干燥和潮湿的退火都能改善 TFT 的一致性,但是潮湿的退火最有效。因此, a-IGZO 的沉积后退火主要在湿氧环境中进行,以改进器件性能和均匀性,以及降低器件性 能对层初始沉积条件的依赖度。

为了稳定 a-IGZO 膜,对于显示器的 TFT,沉积后退火是常规进行的,通常是  $1\sim 2h$ ,温 度范围为 250~350℃,但很少指定退火环境。

## 4) 沉积金属

选择栅极和源/漏确的金属需要考虑下列三点:线电阻、加工性能(包括溅射沉积)和液 晶行业的经验。因此,在某些情况下,用 Mo 或 Ti/Mo 作为反向叠层器件的金属层,需要刻 蚀除去沟道区上的 Mo。如使用 Ti/Mo,则在氧等离子进行选择性刻蚀, Mo 被除去, Ti 则

形成具有保护和刻蚀停止两种功能的 TiO。层。在若 干反平面 TFT 结构中,使用复合的 Ti/Al/Ti 层,在随 后的 a-IGZO 沉积后退火过程中, Ti 将被与它毗邻的 a-IGZO 还原,产生一层富电子高电导率材料,从而减 少金属层和沟道之间的接触电阻。

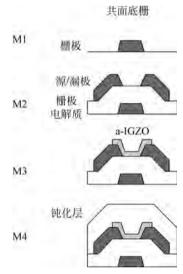

## 5) 工艺流程

反平面 TFT 的四次光刻流程如图 5.4.5 所示。 这四次光刻过程是: 确定栅极金属形状(M1)、确定源/ 漏极金属形状(M2)、确定 a-IGZO 层形状(M3)和通过 顶部钝化层(未示出)确定接触孔形状(M4)。对于 图 5.4.4(a) 所示的反叠层刻蚀停止 TFT, 可比较的阶 段是, 栅极金属的沉积和形状确定(M1); 栅极电介质 的沉积、a-IGZO 和刻蚀停止层的沉积以及刻蚀停止层 形状的确定(M2); a-IGZO 层形状的确定(M3); 源/ 漏极金属的沉积和形状的确定(M4)以及最后的覆盖/

图 5.4.5 反平面 TFT 的工艺流程

钝化层和接触窗口的沉积(M5)。因此,反叠层刻蚀停止结构比反共面的多一次光刻过程。

#### a-IGZO TFT 的件能 5.4.3

## 1. n 沟道性能

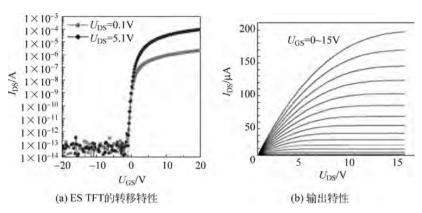

$W=25\mu m$  和  $L=10\mu m$  的反叠层刻蚀停止结构 a-IGZO TFT 的高质量的转移特性如 图 5.4.6(a)所示。该器件的栅极电介质是用 PECVD 方法沉积的 200nm 厚的  $SiO_x$ ,器件 的场效应迁移率是 21cm²/Vs,亚阈值斜率为 0.29V/dec,ON/OFF 比率为 10°。具有 11. 8cm<sup>2</sup>/Vs 饱和迁移率的 a-IGZO TFT 的典型输出特性曲线如图 5.4.6(b)所示,器件显 示了高 $U_D$ 下良好的电流饱和特性,并且在低 $U_D$ 下不出现电流拥挤。

## 2. 传导过程和态密度分布(DOS)

- 1) 与传导过程有关的一些实验结果

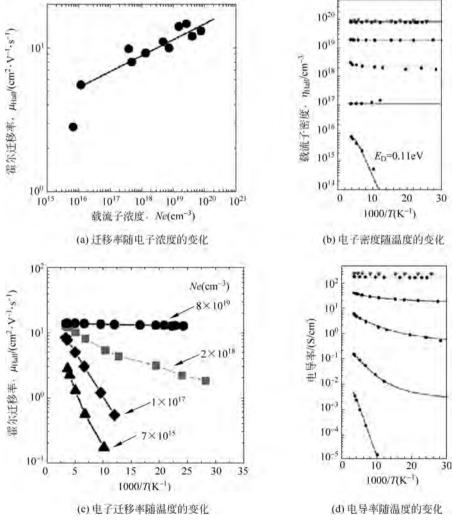

- a-IGZO 膜的一些传导过程的特征已经从掺杂膜的霍尔效应测量获得,如图 5.4.7 所 示。有下列四点结论:

- (1) 关键特性是霍尔迁移率随掺杂浓度上升而增加,如图 5.4.7(a)所示。这与单晶硅 的特性是相反的,在单晶硅中,由于荷电杂质增加和电子之间的散射,迁移率随杂质浓度上 升而下降。

- (2) 如图 5.4.7(b)所示,当载流子密度大于  $10^{17}$  cm<sup>-3</sup> 时,载流子密度与温度无关,表明

高质量 a-IGZO TFT 的特性曲线 图 5.4.6

图 5.4.7 掺杂 a-IGZO 样品的霍尔效应

材料是简单的,其费米能级高于导带边。这也完全不同于因带尾密度足够大费米能级从未 进入导带的 a-Si: H 的特性。在图 5.4.7(b)中轻掺杂材料显示 0.11eV 的低温的活化能,仿 佛材料冻住了处于受主能级陷阱中的电子。

- (3) 如图 5.4.7(c) 所示, 当载流子浓度甚高于  $2 \times 10^{18} cm^{-3}$  时, 霍尔迁移率与温度无 关。而在中等掺杂水平下,迁移率由于热激发是随温度增加而上升。

- (4) 如图 5.4.7(d) 所示, 电导率 σ(是载流子密度和迁移率的乘积) 在掺杂水平高干 3×10<sup>18</sup> cm<sup>-3</sup> 时,与温度无关。在掺杂水平低于 3×10<sup>18</sup> cm<sup>-3</sup> 的中间掺杂水平情况下,受热 激活影响,随温度增加而上升。但电导率 σ 只有在最低载流子浓度下才有单一的激活能。 不存在简单的  $\ln(\sigma)$ 比例于  $T^{-1}$  的阿伦尼乌斯(Arrhenius)关系,而是  $\ln(\sigma)$ 比例于  $T^{-1/4}$ , 类似于低温下态隙中定域态电子的导电。

## 2) 导电机理

氧化物半导体薄膜晶体管(TFT),如 InGaZnO TFT 即使在室温下制造也可以获得高 迁移率。这主要由于离子键结构对键角无序不敏感。然而,这类沟道材料有成分无序,由此 造成在导带最小值(E,,)的上面有一个势垒,这意味着当电子被释放进入导带过程中存在渗 透导电(percolation conduction)。此外,在带隙内存在局域带尾态,意味着存在陷阱限制导 电(trap-limited conduction, TLC)。特别是,氧化物半导体有一个缓坡带尾态,其(kT.)约 为 20meV,小于 300K 下电子的热运动能量为 100~200meV,导致其不同的迁移率表现。

根据上述,导电过程是这样的:受热激发,电子从陷阱逸出到导带,这个过程是陷阱限 制导电。电子进入导带后,由于导带最小值 Em上的势垒起伏,在导带中的传导属于渗透导 电。所以整个导电过程是这两个过程影响因素的乘积,可据此求场效应迁移率(μ<sub>ΕΕ</sub>),从而 推导出有物理意义的 I-U 关系。

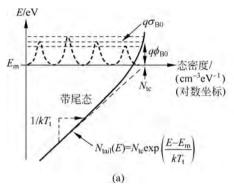

陷阱限制导电(TLC):陷阱限制导电的效应可以用自由载流子密度 $(n_{free})$ 和陷阱中载 流子密度  $(n_{tail})$  的比  $\gamma_{TLC}$  表示,具体表达为  $\gamma_{TLC} = n_{free}/(n_{free} + n_{tail})$ 。其中,  $n_{free} =$  $N_{\rm C} \exp[(E_{\rm F} - E_{\rm m})/kT]$ ,其中  $N_{\rm C}$  是自由载流子的有效密度; kT 是热运动能量。因为在  $kT_{i} < kT_{i}$  带尾态中载流子密度分布  $n_{ini}$  的近似表达如图 5.4.8(a)中所示也是指数分布,即  $n_{\text{tail}} = N_{\text{tc}} k T_{\text{t}} \exp[(E_{\text{F}} - E_{\text{m}})/kT]$ ,其中  $N_{\text{tc}}$  是  $E = E_{\text{m}}$  处的带尾态的密度。由此可见, $n_{\text{tail}}$  如 同 $n_{\text{free}}$ 一样取决于kT,而不取决于带尾态kT,的指数分布。所以指数项在 $\gamma_{\text{TLC}}$ 表达式中互相抵消 了,即

$$\gamma_{\text{TLC}} \equiv \frac{n_{\text{free}}}{n_{\text{free}} + n_{\text{tail}}} \approx \frac{N_{\text{C}}}{N_{\text{C}} + N_{\text{tc}} k T_{\text{t}}}$$

(5.4.1)

渗透导电:与高于 $E_m$ 的势垒相关的渗透导电可以视为无势垒时的带迁移率 $\mu_0$ 乘上一个 缩小的系数。假设势垒为高斯随机分布[如图 5.4.8(b)所示],势垒高度的平均值为 ø Bo ,分 布宽度为 $\sigma_{B0}$ ,则考虑势垒影响后的带迁移率 $\mu_0^* = \mu_0 \exp[-q\phi_{B0}/kT + (q\sigma_{B0})^2/(kT)^2]$ ,热 释放电子使费米能级变小一个量 $(\Delta E_F)$ ,从而等效地减少势垒高度 $\phi_{B0}$ 。热减少的势垒高度 可以表达为  $\phi_{BO} \exp(-\gamma_B \Delta E_F/kT)$ ,其中  $\gamma_B \equiv (D_B - W_B)/D_B$ 。当  $\gamma_B \Delta E_F/kT \ll 1$  时,通过 泰勒级数展开可以近似为  $\phi_{B0}(1-\gamma_{B}\Delta E_{F}/kT)$ 。因此, $\Delta\phi_{B0}=\gamma_{B}\Delta E_{F}/kT$ 。综合考虑上述 因素后,渗透导电的迁移率 μ<sub>Per</sub> 为

$$\mu_{\text{Per}} \equiv \mu_{0} \exp \left[ -\frac{q \left( \phi_{B0} - \Delta \phi_{B} \right)}{kT} + \frac{q \left( \sigma_{B0} \right)^{2}}{2 (kT)^{2}} \right] = \mu_{0}^{*} \exp \left( \frac{\gamma_{B} \Delta E_{F}}{kT} \phi_{B0} \right)$$

(5.4.2)

图 5.4.8 随能量作指数分布的局域带尾态的态密度分布示意[同时,显示势垒高度的平均值( $\phi_{Bo}$ )和分布宽度( $\sigma_{Bo}$ )],以及氧化物半导体 TFT 的渗透与陷阱限制导电组合情况下载流子传输示意 ( $D_B$  和  $W_B$  分别表示势垒的空间距离和宽度)

其中 $\mu_0^* = \mu_0 \exp[-q\phi_{B0}/kT + (q\sigma_{B0})^2/(kT)^2]$ ,被称为有效带迁移率。

在方程(5.4.2)中, $\Delta E_{\rm F}$  是受栅极电压( $U_{\rm GS}$ )控制的。通过求解泊松方程可以推导出它们之间的关系是  $\Delta E_{\rm F} = 2(kT/q)\ln[C_{\rm ox}(U_{\rm GS}-U_{\rm th})/Q_{\rm ref}]$ ,其中  $C_{\rm ox}$  是栅极与绝缘体之间的电容;  $U_{\rm th}$  是阈值电压;  $Q_{\rm ref} \equiv 2\varepsilon$ , $N_c k T \exp[(E_{\rm F0}-E_{\rm m})/(kT)]^{0.5}$ 。将方程(5.4.1)和方程(5.4.2)组合得到陷阱限制和渗透复合迁移率,从而得到组合场效应迁移率( $\mu_{\rm FE}$ )与  $U_{\rm GS}$  的关系式为

$$\mu_{\rm FE} \equiv \mu_{\rm Per} \gamma_{\rm TLC} = \mu_0^* \left( \frac{N_{\rm C}}{N_{\rm C} + N_{\rm to} k T_{\rm t}} \right) \left( \frac{C_{\rm ox}}{Q_{\rm ref}} \right)^{\alpha_{\rm p}} (U_{\rm GS} - U_{\rm th})^{\alpha_{\rm p}}$$

(5.4.3)

可以看到,方程(5.4.3)遵循幂函数规律。在这里, $\alpha_p \equiv 2q\phi_{B0}\gamma_B/kT$ ,与渗透导电有关。 在方程(5.4.3)中,TLC影响常数项,而指数由渗透导电决定。

## 3. 电流电压关系

定义漏极电流  $I_{DS} = \mu_{FE} C_{ox} (U_{GS} - U_{th} - U_{ch}) dU_{ch}/dx$ ,由方程(5.4.3)与  $I_{DS}$  定义加上积分可以推导出  $I_{DS} (U_{GS})$ 。积分范围:x = 0 到 L(沟道长度),沟道电位  $U_{ch} = \emptyset$  0 到  $U_{DS}$ :

$$I_{DS} \equiv \mu_0^* \left( \frac{N_{C}}{N_{C} + N_{tc}kT_{t}} \right) \frac{W}{L'} \frac{C_{ox}^{a_p+1}}{Q_{ref}^{a_p}} (U_{GS} - U_{th})^{a_p+1} U_{DS}'$$

(5.4.4)

方程(5.4.4)表明, $I_{\rm DS}$ 与 $U_{\rm GS}$ 是幂函数关系。在( $U_{\rm GS}-U_{\rm th}$ )》 $U_{\rm DS}$ 时,用二项式展开,可得到线性区表达式。方程(5.4.4)中 $L'=L-\Delta L$ , $\Delta L$ 是沟道延伸;有效的漏极电压 $U'_{\rm DS}=U_{\rm DS}-2R_{\rm C}I_{\rm DS}$ , $R_{\rm C}$ 是接触电阻。对于饱和漏极电流,可用饱和参数( $\beta_{\rm sat}$ )改写它,即在方程(5.7.4)中以 $\beta_{\rm sat}(U_{\rm GS}-U_{\rm th})$ 取代 $U'_{\rm DS}$ 。

## 4. 态密度分布(DOS)

平板显示系统设计的关键需要之一是基于物理上的 TFT 模型,这就需要很好地了解 TFT 的基本的载流子输运机构,特别是态密度和场效应迁移率。AOS 材料具有非晶态相 的导带底起伏,这导致在亚间隙中存在局域态和在导带底上面的势垒,如图 5.4.9(a)、(b) 所示。图 5.4.9(a)所示曲线指出,AOS 的陷阱密度比 α-Si:H 中的小一个量级以上。在能量进入能隙较深处情况下,导带带尾态宽度从 13 meV 变化到 100 meV,这些值都接近或甚至小于室温下热运动能量,这暗示 α-IGZO 将没有结构性的带尾态。在靠近  $E_v$  处,态密度

达到  $10^{20} \sim 10^{21} \,\mathrm{cm}^{-3}$ , 这预示 p 型 α-IGZO TFT 的性能是很差的。图 5.4.9(b)给出的导电 机构指出:由于热激发电子从陷阱中逸出,经过多次落入陷阱又逸出后,进入导带中沿各势 垒谷底绕行,这时属于 TLC 导电。当增加  $U_{GS}$ ,使  $E_F < E_h$  时,电子可以穿越势垒输运,进 入渗透导电。

图 5.4.9 从导带边 $(E_m)$ 到价带边 $(E_v)$ AOS 的态密度随能级变化的典型曲线(作为比较 同图画出 α-Si:H 的态密度分布曲线)以及 AOS 的能带图示意图「包括会引起 TLC 的带尾态和引起渗透导电的在  $E_m$  上的电位起伏(势垒)]

# 习题与思考

- 现在的电视体制已普遍采用 1000×2000,在这种情况下如采用无源矩阵 LCD,则 其驱动裕度 DM 是多少?「提示:利用式(4.4.11)]

- 5.2 独立画出 AM-LCD 的一个驱动单元(液晶像素加 TFT)的示意图,并说明其工作 原理。

- 5.3 仿图 5.1.1, 画出 n 型衬底不同表面电荷下理想的金属-绝缘体-半导体(MIS)的 能带图。

- 实际的 MIS 在不施加栅极电压时都不是平带的,这是哪些因素造成的? 5.4

- 画出反向叠层型 a-Si: H TFT 的两种结构,并比较它们的优缺点。 5.5

- 非晶氧化物的迁移率为什么比 a-Si:H 高一个数量级或更多? 5.6