# 时序逻辑电路

CHAPTER 5

### 兴趣阅读——微处理器发明

特德·霍夫(Ted Hoff)1937年生于美国纽约州,从小就对电子科学产生了浓厚的兴趣。1954年,他进入了美国纽约特洛伊的 Rensselear 综合工学院攻读电子工程专业。在此期间,他发明了电子火车探测器和雷电探测器,并获得了专利。1958年进入了斯坦福大学,后取得了硕士和博士学位。

1968年,霍夫加入 Intel (英特尔)公司,开始从事半导体存储芯片的研究工作。1969年6月的一天,日本 ETI 公司的人员找到霍夫,想请他设计一套极其复杂的计算器芯片。这种设计方案已经超出了当时英特尔公司的业务范围,但霍夫却从方案中得到了启发。于是,"能否以一种微型的通用计算机芯片取代计算器中的整套芯片"的大胆念头渐渐在霍夫脑子中萌生。

霍夫与从仙童公司跳槽来的斯坦·麦卓尔合作,成立了研发小组,研究目标是将一台通用计算机造在一个芯片系统上。霍夫的最大突破是对芯片组织结构的设计,在他的方案中,计算机的"大脑"由四部分组成——中央处理器(CPU)、存储指令的只读存储器(ROM)、存储动态数据的随机存储存取器(RAM)和一个简单的用作输入输出的移位寄存器。就这样,世界上第一台真正可运转的微处理器 4004 在 1971 年问世了,该芯片集成了 2000 个晶体管,处理能力相当于世界上第一台计算机。之后相继推出了 8 位微处理器 8008、8080 和 IBM 采用的芯片8088,乃至后来的 80X86、Pentium 系列芯片,微处理器市场开始红火起来,霍夫为英特尔和全世界的微处理器领域做出了无可替代的贡献。

我国微处理器技术研究起步较晚但发展很快,龙芯中科技术股份有限公司自主研发的龙芯3C5000L处理器与目前市场中主流 CPU 之间的差距已经越来越小,甚至可以满足云计算和数据中心性能要求。我国2015年发射的北斗卫星首次使用了"龙芯"微处理器。

图 5-1 是霍夫和他发明的微处理器及中国"龙芯"系列微处理器。

(a) 霍夫

(b) 霍夫发明的微处理器

(c) 中国"龙芯"系列微处理器

图 5-1 霍夫和他发明的微处理器及中国"龙芯"系列微处理器

本章首先介绍时序逻辑电路在逻辑功能和电路结构上的特点,然后着重讨论时序逻辑电 路的分析和设计方法,最后分别介绍了寄存器和计数器这两类常用的时序逻辑电路。此外,还 给出了用 Multisim 和 VHDL 分析设计时序逻辑电路的实例。本章学习要求如下:

- (1) 理解时序逻辑电路在逻辑功能及电路结构上的特点:

- (2) 熟悉时序逻辑电路逻辑功能的描述方法:

- (3) 掌握时序逻辑电路的一般分析方法:

- (4) 掌握同步时序逻辑电路的设计方法,能设计简单的同步时序逻辑电路;

- (5) 掌握寄存器的结构和工作原理;

- (6) 掌握集成计数器的结构、工作原理和使用方法:

- (7) 了解用 Multisim 和 VHDL 分析设计时序逻辑电路的方法。

#### 5.1 概述

#### 时序逻辑电路的基本概念 5.1.1

从对组合逻辑电路的讨论中可知,组合逻辑电路任一时刻的输出仅仅取决于当前时刻的 输入,与之前各时刻的输入无关。除此之外,还有一类逻辑电路,它在任一时刻的输出不仅与 当前时刻的输入有关,还与电路原来的状态有关,具备这种特点的逻辑电路称为时序逻辑电 路, 简称时序电路。

### 1. 时序电路的一般模型和结构特点

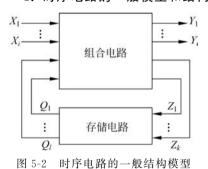

因为时序电路的输出与电路原来的状态有关,所以在 时序电路中,除了有能反映当前各输入状态的组合电路之 外,还应该有能够记住电路原来状态的存储电路,因此时 序电路由组合电路和起记忆作用的存储电路两部分组成, 其中存储电路一般由各类触发器组成。时序电路的一般 结构模型如图 5-2 所示。

图 5-2 中, $X(X_1, X_2, \dots, X_i)$ 为组合电路的(外部)输 入信号;  $Y(Y_1,Y_2,\dots,Y_r)$ 为组合电路的(外部)输出信号;

$Z(Z_1, Z_2, \cdots, Z_k)$ 为存储电路的输入信号;  $Q(Q_1, Q_2, \cdots, Q_k)$ 为存储电路的输出信号。这些信 号之间的逻辑关系可以用下面三组方程表示

$$Y = F(X, Q) \tag{5-1}$$

$$Z = G(X, Q) \tag{5-2}$$

$$Q^{n+1} = H(X,Q) \tag{5-3}$$

式(5-1)称为输出方程;式(5-2)称为驱动方程或激励方程;式(5-3)称为状态方程。其中:Q 为存储电路当前时刻的输出信号,称为存储电路的现态;  $Q^{n+1}$  为现态 Q 和输入信号 X 共同作 用下存储电路建立的新状态,称为存储电路的次态。

### 2. 时序电路的分类

时序电路的类型很多,有不同的分类方法。

(1) 根据触发器的动作特点不同,时序电路可以分为同步时序电路和异步时序电路两类。 若时序电路中,所有触发器状态的变化是在同一时钟信号作用下同时发生的,就称为同步 时序电路。

若时序电路中,没有统一的时钟信号,各触发器状态的变化不是同时发生的,而是有先有后的,这类时序电路称为异步时序电路。

(2) 根据输出信号的特点可以将时序电路分为米里(Mealy)型和摩尔(Moore)型两类。

若时序电路的输出不仅与电路的现态有关,还与该时刻的输入有关,则这类时序电路称为 米里型时序电路。

若时序电路的输出仅与电路的现态有关,而与当前时刻的输入无关,或者根本就不存在独立设置的输出,而是以电路的状态作为输出,则这类时序电路称为摩尔型时序电路。

(3)根据电路实现的逻辑功能不同,时序电路可以分为计数器、寄存器、顺序脉冲发生器、读/写存储器等类型。

### 5.1.2 时序逻辑电路的功能描述方法

由于组合电路和时序电路的结构、性能不同,因此在逻辑功能的描述方法上也有所不同。时序电路逻辑功能的描述方法除逻辑表达式外,还有用来描述时序电路状态转换全过程的状态转换表、状态表、状态转换图和时序图等。

### 1. 逻辑表达式

用于描述时序电路功能的逻辑表达式为输出方程、驱动方程和状态方程,如式(5-1)~式(5-3)所示。

### 2. 状态转换表

状态转换表,也称为状态转换真值表,是用列表的方式描述时序电路输出、次态与电路输入、现态之间的逻辑关系。具体做法是,把时序电路的输入和现态的各种可能取值,代入状态方程和输出方程进行计算,求出相应的次态和输出,将全部的计算结果列成真值表的形式,就得到了状态转换表,其结构如表 5-1 所示。

表 5-1 时序电路的状态转换表

| $X_1, X_2, \cdots, X_i$ | $Q_r \cdots Q_1 Q_0$ | $Q_r^{n+1} \cdots Q_1^{n+1} Q_0^{n+1}$ | $Y_1, Y_2, \cdots, Y_j$ |

|-------------------------|----------------------|----------------------------------------|-------------------------|

|                         |                      |                                        |                         |

#### 3. 状态表

状态表是由状态转换表转化而来的。对米里型时序电路,其表的第一行为输入X的各种可能取值,表的第一列为现态S,表的中间部分表示在相应输入和现态作用下时序电路的次态 $S^{n+1}$ 和当前输出Y,其结构如表 5-2 所示。对摩尔型时序电路,因为输出与输入无关,所以可将输出放在最后一列,只和状态建立关系,其结构如表 5-3 所示。状态表能更直观、更清晰地反映出时序电路的状态转换关系。

表 5-2 米里型时序电路的状态表

| C | $S^{n+1}/Y$ |           |     |           |

|---|-------------|-----------|-----|-----------|

| 3 | $x = x_1$   | $x = x_2$ | ••• | $x = x_n$ |

|   |             |           |     |           |

表 5-3 摩尔型时序电路的状态表

| c | $S^{n+1}$ |           |  |           |

|---|-----------|-----------|--|-----------|

| 3 | $x = x_1$ | $x = x_2$ |  | $x = x_n$ |

|   |           |           |  |           |

### 4. 状态转换图

为了能更形象直观地表示出时序电路的状态转换规律,还可以将状态表的内容用图形的

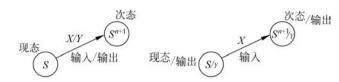

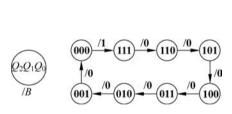

方式表示,即状态转换图(简称状态图)。时序电路状态图的画法与触发器状态图的画法一致,即以圆圈表示时序电路的各种状态,以箭头线表示状态转换方向。同时,在箭头线旁注明状态转换前的输入变量 X 的取值和输出变量 Y 的值。通常将 X 的取值标在斜线以上,将 Y 的值标在斜线以下。如果没有输入或输出信号,则对应的位置上为空,如图 5-3(a)所示。

(a) 米里型时序电路的状态图

(b) 摩尔型时序电路的状态图

图 5-3 时序电路的状态图

图 5-3(a)是适用于米里型时序电路的状态图。对于摩尔型时序电路,其状态图也可用图 5-3(a)表示,由于电路输出只与现态有关,与输入无关,所以在绘制状态图时,输出可以不标注在箭头线旁,可与状态一起标注在圆圈中,中间用斜线分隔,通常斜线以上标状态值,斜线以下标 Y 值,如图 5-3(b)所示。

### 5. 时序图

时序图又称为工作波形图,是描述时序电路在输入信号和时钟脉冲序列作用下,电路状态 及输出随时间变化的波形图,其画法与触发器时序图的画法一致。

以上各个功能描述方法都可以用来描述同一个时序电路的逻辑功能,这些描述方法在本质上是相同的,所以它们之间可以相互转换。

## 5.2 同步时序电路的分析

所谓同步时序电路的分析,就是指出给定同步时序电路的逻辑功能。其关键是找出同步时序电路在输入信号及时钟信号作用下,电路的状态及输出的变化规律。

## 5.2.1 同步时序电路的分析方法

同步时序电路的分析过程一般可归纳为如下几个步骤:

- (1) 根据给定的时序电路,列出时序电路的输出方程和各触发器的驱动方程;

- (2)将触发器的驱动方程代入各自的特性方程,求出各触发器的次态方程,从而得到时序 电路的状态方程;

- (3) 根据求得的状态方程和输出方程,列出时序电路的状态转换表;

- (4) 根据状态转换表列出状态表,画出状态图或时序图:

- (5) 总结分析时序电路的逻辑功能。

以上步骤是分析时序电路的一般步骤,实际分析过程中,可以根据电路的具体情况灵活运用,而没有严格的固定程序。

## 5.2.2 同步时序电路分析举例

以下通过实例来阐述同步时序电路的分析方法。

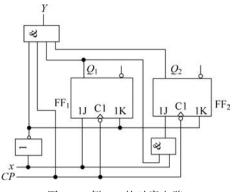

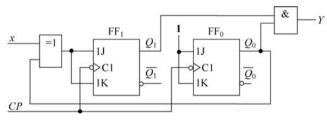

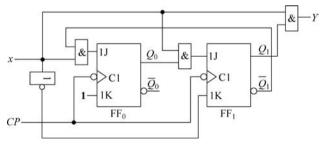

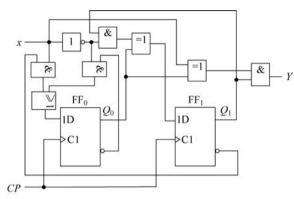

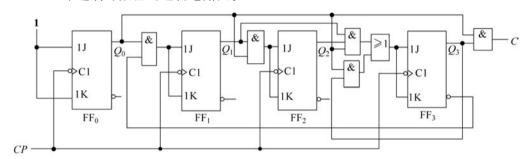

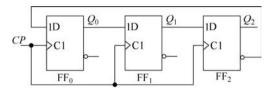

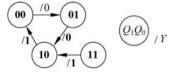

【例 5-1】 时序电路如图 5-4 所示,试分析该电路。

(1) 列出时序电路的输出方程和驱动方程;

- (2) 求出电路的状态方程;

- (3) 列出电路的状态转换表:

- (4) 列出状态表,画出状态图,当输入序列 x = 1100110 时,求出输出序列 Y;

- (5) 指出电路的类型和逻辑功能。

解: 由图 5-4 可知,该电路由门电路和 JK 触发器组成。电路的输入为x、输出为 Y。输出 Y 与输入x 和状态 Q 均有关系,而且两个触发器共用一个时钟脉冲。所以,该电路是米里型同步时序电路。

(1) 列出同步时序电路的输出方程和驱动方程。

图 5-4 例 5-1 的时序电路

$$Y = \bar{x}Q_1Q_2$$

(这里省略了  $CP$ )

$$\begin{cases} J_1 = x, & K_1 = \bar{x} \\ J_2 = xQ_1, & K_2 = \bar{x} \end{cases}$$

(2) 将驱动方程式代入 JK 触发器的特性方程,求出时序电路的状态方程。

$$Q_1^{n+1} = J_1 \overline{Q_1} + \overline{K_1} Q_1 = x \overline{Q_1} + x Q_1 = x$$

$$Q_2^{n+1} = J_2 \overline{Q_2} + \overline{K_2} Q_2 = x Q_1 \overline{Q_2} + x Q_2 = x (Q_1 + Q_2)$$

- (3) 根据状态方程和输出方程列出时序电路的状态转换表,如表 5-4 所示。

- (4) 根据状态转换表列出状态表, 画出状态图。

电路的状态表如表 5-5 所示,表中的第一行为该时序电路输入 x 的两种可能取值,表中第一列 S 为该时序电路的四种现态,即设  $S_0 = \mathbf{00}$ , $S_1 = \mathbf{01}$ , $S_2 = \mathbf{10}$ , $S_3 = \mathbf{11}$ 。表的中间部分表示在相应的输入 x、现态 S 及 CP 脉冲的作用下建立的次态  $S^{n+1}$  和输出 Y。

| x | $Q_2$ | $Q_1$ | $Q_{2}^{n+1}$ | $Q_1^{n+1}$ | Y |

|---|-------|-------|---------------|-------------|---|

| 0 | 0     | 0     | 0             | 0           | 0 |

| 0 | 0     | 1     | 0             | 0           | 0 |

| 0 | 1     | 0     | 0             | 0           | 0 |

| 0 | 1     | 1     | 0             | 0           | 1 |

| 1 | 0     | 0     | 0             | 1           | 0 |

| 1 | 0     | 1     | 1             | 1           | 0 |

| 1 | 1     | 0     | 1             | 1           | 0 |

| 1 | 1     | 1     | 1             | 1           | 0 |

表 5-4 例 5-1 的状态转换表

表 5-5 例 5-1 的状态表

| S                 | $S^{n+1}/Y$                      |                                                                                                          |  |

|-------------------|----------------------------------|----------------------------------------------------------------------------------------------------------|--|

| 3                 | x = 0                            | x = 1                                                                                                    |  |

| $S_0$             | $S_{\scriptscriptstyle 0}/{f 0}$ | $S_1/{f 0}$                                                                                              |  |

| ${oldsymbol S}_1$ | $S_{\scriptscriptstyle 0}/0$     | $S_3/0$                                                                                                  |  |

| ${S}_{z}$         | $S_{_0}/0 \ S_{_0}/0 \ S_{_0}/0$ | $S_3/0$                                                                                                  |  |

| $S_3$             | $S_0/1$                          | $egin{array}{c} S_1/0 & & & & & \\ S_3/0 & & & & & \\ S_3/0 & & & & & \\ S_3/0 & & & & & \\ \end{array}$ |  |

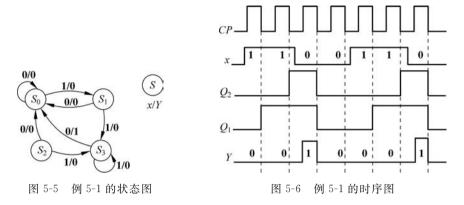

为了更清楚地表示出状态的变化规律,还可以根据状态表画出状态图,如图 5-5 所示。

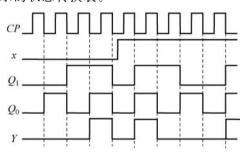

当输入序列 x = 1100110 时,对应的时序图如图 5-6 所示。从图中可以看出,输出序列 Y = 0010001。

【注意】 时序图中Y的脉冲与时钟脉冲等宽,原因是Y的表达式中实际上含有CP。

(5) 由状态图 5-5 可知,当输入一个 1 时,电路转到  $S_1$  状态;当输入两个 1 时,电路转到  $S_3$  状态;当第三个输入为 0 时,电路回到  $S_0$  状态,且输出一个 1。结合时序图中的输出序列,故该电路是 110 序列检测器,当输入序列中出现连续的 110 时,输出为 1,否则输出为 0。图中状态  $S_2$  是多余状态。

【提示】 状态表和状态图中字母表示的状态可直接用代码组合表示,此时 S 写为  $Q_2Q_1$ ,  $S^{n+1}$  写为  $Q_2^{n+1}Q_1^{n+1}$ 。

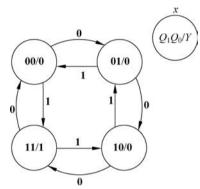

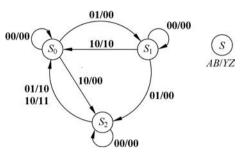

【例 5-2】 分析如图 5-7 所示电路,写出驱动方程、输出方程和状态方程,给出状态转换表和状态图。

图 5-7 例 5-2 的时序电路

解:由图 5-7 可知,该电路是由门电路和 JK 触发器组成的同步摩尔型时序电路。

(1) 列出电路的驱动方程和输出方程。

$$\begin{cases}

J_1 = K_1 = x \oplus Q_0 \\

J_0 = K_0 = 1

\end{cases}$$

$$Y = Q_1 Q_0$$

(2) 将驱动方程代入 JK 触发器的特性方程,得状态方程为

$$\begin{vmatrix} Q_1^{n+1} = J_1 \overline{Q_1} + \overline{K_1} Q_1 = (x \oplus Q_0) \overline{Q_1} + \overline{x \oplus Q_0} Q_1 = x \oplus Q_0 \oplus Q_1 \\ Q_0^{n+1} = J_0 \overline{Q_0} + \overline{K_0} Q_0 = \overline{Q_0} \end{vmatrix}$$

(3) 列出电路的状态转换表,如表 5-6 所示。

| x | $Q_{\scriptscriptstyle 1}$ | $Q_{0}$ | $Q_1^{n+1}$ | $Q_0^{n+1}$ | Y |

|---|----------------------------|---------|-------------|-------------|---|

| 0 | 0                          | 0       | 0           | 1           | 0 |

| 0 | 0                          | 1       | 1           | 0           | 0 |

| 0 | 1                          | 0       | 1           | 1           | 0 |

| 0 | 1                          | 1       | 0           | 0           | 1 |

| 1 | 0                          | 0       | 1           | 1           | 0 |

| 1 | 0                          | 1       | 0           | 0           | 0 |

| 1 | 1                          | 0       | 0           | 1           | 0 |

| 1 | 1                          | 1       | 1           | 0           | 1 |

|   |                            |         |             | •           |   |

表 5-6 例 5-2 的状态转换表

图 5-8 例 5-2 的状态图

设计要求的最简时序电路。

(4) 由表 5-6 可以画出状态图,如图 5-8 所示。

在逻辑电路的分析过程中,首先应根据给定的逻辑电路,分析电路组成,从而判断属于哪种逻辑电路,进而采用正确的分析方法进行分析。在分析过程中也要根据电路的实际情况,合理选择各种逻辑功能的描述方法。

## 5.3 同步时序电路的设计

时序电路的设计,也称为时序电路的综合,就是根据给定的逻辑功能要求,选择适当的逻辑器件,设计出符合

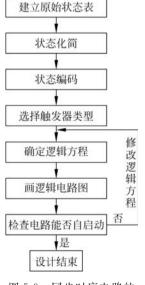

## 5.3.1 同步时序电路的设计方法

### 1. 同步时序电路的设计步骤

同步时序电路设计的一般步骤如图 5-9 所示。

(1)建立原始状态表。通常,所要设计的同步时序电路的逻辑功能是通过文字、图形或波形来描述的,首先必须将它们变换成规范的状态图或状态表。这种直接从文字描述得到的状态图或状态表称为原始状态图或原始状态表。

具体做法是: 首先根据设计要求,确定输入变量、输出变量及 电路应包含的状态数,然后定义输入、输出逻辑状态和每个电路状态的含义,最后按照设计要求建立原始状态图,进而建立原始状态 表(也可直接建立原始状态表)。

(2) 状态化简。原始状态表(或图)中可能包含多余的状态,消除多余状态的过程称为状态化简。状态化简是建立在等价状态基础上的。如果两个状态在相同的输入条件下有同样的输出,并转换到同一个次态,那么这两个状态就称作等价状态。显然等价状态是重复的,可以合并成一个状态。合并等价状态可以削去多余的状态,以便建立最简状态表(或图)。

微课视频

图 5-9 同步时序电路的 一般设计步骤

- (3) 状态编码。给最简状态表中的每一个状态指定一个特定的二进制代码,形成编码状 态表的过程称为状态编码,也称为状态分配。编码方案不同,设计出的时序电路结构也就 不同。

- (4) 选择触发器类型。不同触发器的驱动方式不同,选用不同的触发器设计出的时序电 路是不一样的。因此,在设计具体时序电路之前,必须选定触发器的类型。

- (5) 确定逻辑方程。根据编码状态表和选定的触发器类型,写出时序电路的状态方程、驱 动方程和输出方程。

- (6) 画逻辑电路图。根据得到的驱动方程和输出方程,画出逻辑电路图。

- (7) 检查电路能否自启动。有些同步时序电路设计中会出现没用的无效状态,当电路上 电后可能会进入这些无效状态而无法退出。因此,同步时序电路设计的最后一步必须检查所 设计的电路能否进入有效状态,即是否具有自启动的能力。如果不能自启动,则需修改逻辑方 程,再根据修改后的逻辑方程画逻辑电路图。

### 2. 建立原始状态表

从文字描述的设计要求建立原始状态表是同步时序电路设计的第一步,是后面所有设计 工作的基础。但迄今为止,还没有一个系统的方法可以遵循,主要依赖设计者的经验和对设计 任务的理解。

建立原始状态表,实质上就是要确定电路应具备哪些状态及如何进行状态转换,进而得到 设计者要求的输入、输出时序关系。因此在建立原始状态图(或表)时,应关注的是正确性,尽 可能不要遗漏任何一个状态,至于状态是否多余,此时不必注意。

常用的建立原始状态表的方法是:

- (1) 分析给定的设计要求,确定输入变量和输出变量。

- (2) 先假定一个初杰,从这个初杰开始,每加入一个输入,就可以确定其次杰(该次杰可能 是已有现态本身,也可能是已有的另一个状态,或者是一个新的状态)和输出。这个过程一直 继续下去, 直到每个现态向其次态的转换都被考虑到, 且不再构成新的状态为止。这样就建立 了所需的原始状态图。

- (3) 根据原始状态图建立原始状态表。

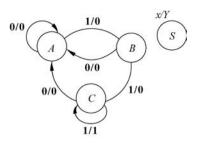

【例 5-3】 试列出 111 序列检测器的状态表。

解:根据设计要求,电路应有一个串行输入端x,用来输入信号序列:一个串行输出端Y, 用来指示对 111 序列的检测结果。输入和输出之间的关系是输入连续的 111 时,输出为 1,其 余情况输出均为 0。则有

输入序列 x:0 1 1 1 输出序列 Y: 0  $0 \quad 0 \quad 1$ 对应状态 S:A B C C

设初态为A,若第一个输入为x=0,不属于要检测的序列,电路停留在状态A上;若 x=1,电路从状态 A 转入状态 B。在状态 B 下,若 x=0,电路返回状态 A; 若 x=1,电路从 状态 B 转入状态 C。在状态 C 下,若 x=0,电路返回状态 A;若 x=1,电路状态停留在状态 C。根据分析结果可画出状态图,如图 5-10 所示。

由状态图可作出状态表如表 5-7 所示。

| 厨 「 10 | Ital | F 0 | 44 44 44 |

|--------|------|-----|----------|

| 图 5-10 | 191  | J-3 | 的状态图     |

| 14. 5 7 P/ 5 5 HJ / N 16. 14. |             |             |  |

|-------------------------------|-------------|-------------|--|

| S                             | $S^{n}$     | r +1 /Y     |  |

| 3                             | x = 0       | x = 1       |  |

| A                             | A/0         | B/ <b>0</b> |  |

| B                             | A/ <b>0</b> | C/ <b>0</b> |  |

| C                             | A/0         | C/1         |  |

表 5-7 例 5-3 的状态表

【例 5-4】 有一代码检测器,用以检测串行输入的 8421 码,其输入的顺序是先低位后高 位,当出现无效码(即输入1010,1011,1100,1101,1110,1111)时,电路的输出为1。试建立该 代码检测器的原始状态图和原始状态表。

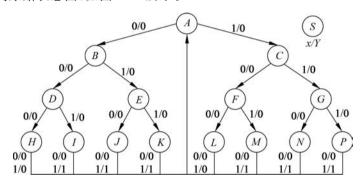

解:根据设计要求,该电路有一个输入x和一个输出Y。由于输入的8421码是先低位后 高位,因此,在判断输入码是否为无效码时,也应从低位到高位检测各位的输入值。设状态 A为初始状态;状态 B 和状态 C 表示最低一位代码分别取 0 和 1 两种情况;状态 D, E, F, G 分 别表示低两位代码的四种不同取值,即  $00\sim11$ ;状态 H,I,J,K,L,M,N,P 分别表示低三 位代码的八种不同取值,即000~111。

当 x 输入的第四位代码到来时,电路即可对输入码进行判断,若出现无效码,检测器输出 为 1, 否则为 0。当 4 位代码检测完成后, 应能返回原始状态 A, 以便下一组代码的检测。根据 分析结果,可得到原始状态图,如图 5-11 所示。

图 5-11 例 5-4 的原始状态图

由原始状态图可转换出原始状态表,如表 5-8 所示。

| Č. | $S^{n-1}$   | ·1/Y        |

|----|-------------|-------------|

| S  | x = 0       | x = 1       |

| A  | B/ <b>0</b> | C/0         |

| B  | D/ <b>0</b> | E/0         |

| C  | F/ <b>0</b> | G/ <b>0</b> |

| D  | H/ <b>0</b> | I/0         |

| E  | J/ <b>0</b> | K/0         |

| F  | L/ <b>0</b> | M/ <b>0</b> |

| G  | N/ <b>0</b> | P/ <b>0</b> |

表 5-8 例 5-4 的原始状态表

| S | $S^{n+1}/Y$ |             |  |

|---|-------------|-------------|--|

| 3 | x = 0       | x=1         |  |

| Н | A/ <b>0</b> | A/0         |  |

| I | A/ <b>0</b> | A/1         |  |

| J | A/ <b>0</b> | A/1         |  |

| K | A/ <b>0</b> | A/1         |  |

| L | A/ <b>0</b> | A/ <b>0</b> |  |

| M | A/ <b>0</b> | A/1         |  |

| N | A/ <b>0</b> | A/1         |  |

| P | A/ <b>0</b> | A/1         |  |

在时序电路的设计过程中,原始状态表的建立方法并不是唯一的,只要能够正确建立原始 状态表(图),即使比较复杂的方法也没有关系,因为在后续的状态化简中,多杂的状态就会被 消掉。

### 3. 状态化简

建立原始状态表时,为避免状态遗漏,可能会引入多余的状态。为了使设计出的电路更简 单,就必须将原始状态表中的多余状态消除掉。消除多余状态的过程称为状态化简。

时序电路的状态表有完全定义和不完全定义两种类型。完全定义的状态表中,状态和输 出值都是完全确定的。不完全定义状态表中,部分次态和输出值不能完全确定,需要在设计中 逐步加以确定。下面以完全定义状态表的化简为例,介绍状态表的化简方法。

完全定义状态表的化简可以通过合并等价状态来实现。在介绍具体的化简方法之前,先 介绍几个概念。

- (1) 等价状态: 是指能满足以下条件的两个状态  $S_i$  和  $S_i$ , 记为 $\{S_i, S_i\}$ 。

- ① 在各种输入取值下,输出完全相同。

- ② 在各种输入取值下,次态满足下列条件之一:

- 两个次态完全相同;

- 两个次态为其现态本身或交错:

- 两个次态为状态对循环中的一个状态对:

- 两个次态的某一后续状态对可以合并。

- (2) 等价状态的传递性: 若状态  $S_i$  和  $S_j$  等价,状态  $S_j$  和  $S_m$  等价,则状态  $S_i$  必和  $S_m$  等 价,记为 $\{S_i,S_i\}\{S_i,S_m\}\rightarrow\{S_i,S_m\}$ 。

- (3) 等价类: 是指彼此等价的状态构成的集合。如,若有 $\{S_i, S_i\}$ 和 $\{S_i, S_m\}$ ,则有等价 类 $\{S_i, S_i, S_m\}$ 。

- (4) 最大等价类: 不能被其他任何等价类包含的等价类。

状态表化简的根本任务就是从原始状态表中找出最大等价类,并用一个状态代替。确定 最大等价类最常用的方法是隐含表法。

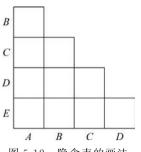

隐含表是一种斜边为阶梯形的直角三角形表格。该表格两个直角边上的方格数目相等, 等于原始状态数减 1。隐含表的纵向由上到下、横向从左到右均按照原始状态表中的状态顺 序标注,但纵向"缺头",横向"少尾"。表中的每个小方格用来表示相应的状态对之间是否存在 等价关系。如图 5-12 所示就是根据具有  $A \setminus B \setminus C \setminus D \setminus E$  这五个状态的原始状态表作出的隐

### 含表。

利用隐含表化简完全定义状态表的步骤如下:

- (1) 构造隐含表,并在表中每个方格中标明相应状态对是否 等价。

- ① 状态对肯定不等价的,在隐含表相应方格中标注"×";

- ② 状态对肯定等价的,在隐含表相应方格中标注"√";

- ③ 状态对条件等价的,在隐含表相应方格中标注等价条件。

- (2) 顺序比较。先将隐含表中所有的状态按照一定顺序对照 原始状态表逐一进行比较,并将比较结果按上面的约定标注在隐含 表中每一个小方格内。

图 5-12 隐含表的画法

- (3) 关联比较。追查填有等价条件的那些方格,若发现所填的等价条件肯定不能满足,就 在该方格右上角加一个"×"。

- (4)确定原始状态表的最大等价类。从隐含表的最右边开始,逐列检查各个小方格,凡是未打"×"的方格,都代表一个等价状态对。彼此等价的几个状态可合并到一个等价类中,最终形成若干个最大等价类。如果有的状态没有包含在任何一个最大等价类中,则该状态自己就是一个最大等价类。

- (5) 建立最简状态表。将每个最大等价类用一个状态来代替,将这种替代关系应用于原始状态表,并删除多余行,就得到了最简状态表。

【例 5-5】 试化简表 5-9 所示的原始状态表。

$S^{n+1}/Y$  $\boldsymbol{S}$ x = 0x = 1A $C/\mathbf{0}$ B/1В  $F/\mathbf{0}$ A/1C $D/\mathbf{0}$  $G/\mathbf{0}$ DD/1 $E/\mathbf{0}$ Ε  $C/\mathbf{0}$ E/1F $D/\mathbf{0}$  $G/\mathbf{0}$ G $C/\mathbf{1}$  $D/\mathbf{0}$

表 5-9 例 5-5 的原始状态表

- 解:(1)作隐含表如图 5-13 所示。

- (2) 顺序比较。从原始状态表中可看出,状态 C 和状态 F 在 x=0 和 x=1 时,它们的输出及次态均相等,因此 C 和 F 是等价状态对,在隐含表中 C 和 F 交叉的方格中画" $\checkmark$ "。此外,A、B 等价的条件是 C、F 等价,A、E 等价的条件是 B、E 等价的条件是 A、E 等价的条件是 A0、A1、A2 等价的条件是 A3、A3 等价的条件是 A4、A5 等价的条件是 A5、A6 等价的条件是 A6、A7 等价的条件是 A8 等价的条件是 A8 等价的条件是 A9 等价的条件是 A9 等价的条件是 A1 和 A2 等价的条件是 A3 等价的条件是 A4 和 A5 等价的条件是 A6 等价的条件是 A7。

- (3) 关联比较。状态对  $A \setminus B$  等价的条件是  $C \setminus F$  等价,而  $C \setminus F$  的确是等价状态对,因此  $A \setminus B$  等价的条件满足。同理,状态对  $A \setminus E$  和状态对  $B \setminus E$  等价的条件也满足;状态对  $D \setminus G$  等价的条件是  $C \setminus D$  和  $D \setminus E$  分别等价,但是从图 5-13 可以看出, $C \setminus D$  和  $D \setminus E$  均不等价,因

此,D、G、等价条件不满足,D、G.不等价,在相应小方格的右上 角加"×"。

- (4) 确定原始状态表的最大等价类。隐含表中未打"×"的 方格都代表一个等价状态对。根据图 5-13 可以得到全部等价 对: $\{A,B\}$ , $\{A,E\}$ , $\{B,E\}$ , $\{C,F\}$ 。因此可得到最大等价类  $\{A,B,E\},\{C,F\},\{D\},\{G\},\{G\}\}$

- (5) 建立最简状态表。令  $a = \{G\}, b = \{C, F\}, c = \{A, B\}$ E},d={D},并将这种替代关系应用于表 5-9 所示的原始状态 表,便可得到其最简状态表,如表 5-10 所示。

| Č. | $S^{n+1}$   | /Y          |

|----|-------------|-------------|

| S  | 0           | 1           |

| а  | b/1         | d/ <b>0</b> |

| b  | d/ <b>0</b> | a/ <b>0</b> |

| С  | b/ <b>0</b> | c/1         |

| d  | d/1         | c/ <b>0</b> |

表 5-10 例 5-5 的最简状态表

【提示】 在进行同步时序电路设计时, 若所建立的原始状态表较简单时, 可以直接采用观 察法对状态表进行化简。

### 4. 状态编码

建立最简状态表后,要设计的同步时序电路所需的状态数 N 就被确定下来,进而电路所 需要的触发器个数 K 也被确定下来,K 和 N 应满足下列关系:

$$2^{K-1} < N \leqslant 2^K \tag{5-4}$$

状态编码是给最简状态表中用字母表示的 N 个状态分别指定一个二进制代码的过程,该 代码就是这 K 个触发器的状态组合。一般而言,采用的编码方案不同,设计出的时序电路的 复杂程度也不同。状态编码的主要任务有两个:一是根据设计所要求的状态数,确定触发器 的个数;二是找到一种合适的状态编码方案,使依据该方案所设计的时序电路最简。

当状态数 N 和触发器的个数(即二进制代码的位数)K 确定以后,状态编码的方案数 M也被确定下来,即

$$M = \frac{2^{\kappa}!}{(2^{\kappa} - N)!}$$

(5-5)

M 的数目将随着 K 的增加而急剧增大。在这种情况下,想要对全部编码方案进行——对 比,从中选取最佳方案是十分困难的。因此,在实际工作中常采用经验法,按一定原则进行状 态编码,来获得接近最佳的方案。其基本思想是:在选择状态编码时,尽可能使状态函数和输 出函数在卡诺图上1方格的分布为相邻,以便形成更大的包围圈,从而有利于状态函数和输出 函数的化简。

状态编码依据的原则为:

- (1) 相同输入条件下,次态相同,现态应给予相邻编码。所谓相邻编码,就是指各二进制 代码中只有一位代码不同。

- (2) 在不同输入条件下同一现态的各个次态编码应相邻。

(3) 输出相同,现态编码应相邻。

【例 5-6】 对表 5-11 所示的状态表进行状态编码。

表 5-11 例 5-6 的状态表

| s | $S^{n+1}/Y$ |             |  |

|---|-------------|-------------|--|

|   | x = 0       | x=1         |  |

| A | C/ <b>0</b> | D/ <b>0</b> |  |

| В | C/0         | A/ <b>0</b> |  |

| C | B/ <b>0</b> | D/ <b>0</b> |  |

| D | A/1         | B/ <b>1</b> |  |

**解**: 状态  $A \sim D$  的编码确定过程如下:

根据编码原则(1),状态 A 和B,A 和C 应分别给予相邻编码。

根据编码原则(2),状态 C 和 D, A 和 C, B 和 D, A 和 B 应分别给予相邻编码。

根据编码原则(3),状态 A,B 和 C 应分别给予相邻编码。

综合上面的分析结果,状态 A 和 B,A 和 C,一定要取相邻编码,可利用卡诺图表示上述相邻要求的状态编码方案,如图 5-14 所示。

这样就可以确定  $A \sim D$  的状态编码方案为

$$A = 00$$

,  $B = 01$ ,  $C = 10$ ,  $D = 11$

图 5-14 例 5-6 的状态

分配方案

代入表 5-11 可得到如表 5-12 所示的编码状态表。需要指出的是,该编码方案不是唯一的。

表 5-12 例 5-6 的编码状态表

| $Q_1Q_0$ | $Q_1^{n+1}Q_0^{n+1}/Y$ |      |  |  |

|----------|------------------------|------|--|--|

|          | x = 0                  | x=1  |  |  |

| 00       | 10/0                   | 11/0 |  |  |

| 01       | 10/0                   | 00/0 |  |  |

| 10       | 01/0                   | 11/0 |  |  |

| 11       | 00/1                   | 01/1 |  |  |

## 5.3.2 同步时序电路设计举例

【例 5-7】 用门电路和 D 触发器设计一个同步串行加法器,实现最低位在前的两个串行二进制整数相加,输出为最低位在前的两个数之和。

解: (1) 建立原始状态表。设 $x_1$  和  $x_2$  为加数和被加数的串行输入,Y 为两数之和的串行输出。两数相加的结果有两种可能: 一种是无进位,一种是有进位。故电路需要两个内部状态,即无进位状态和有进位状态,分别设为 a 和 b 。建立的原始状态图如图 5-15 所示。

图 5-15 例 5-7 的状态图

由图 5-15 可以得到原始状态表,如表 5-13 所示。

| S | $S^{n+1}/Y$    |                |                |                |  |  |

|---|----------------|----------------|----------------|----------------|--|--|

|   | $x_2 x_1 = 00$ | $x_2 x_1 = 01$ | $x_2 x_1 = 10$ | $x_2 x_1 = 11$ |  |  |

| а | a/ <b>0</b>    | a/1            | a/1            | b/ <b>0</b>    |  |  |

| b | a/1            | b/ <b>0</b>    | b/ <b>0</b>    | b/ <b>1</b>    |  |  |

表 5-13 例 5-7 的状态表

- (2) 状态化简。由表 5-13 可知,该状态表不能再化简,为最简状态表。

- (3) 状态编码。电路有两个状态,故选一个触发器,设a = 0, b = 1,代入表 5-13 得编码状 态表,如表 5-14 所示。

| 0 | $Q^{n+1}/Y$    |                |             |                |  |  |

|---|----------------|----------------|-------------|----------------|--|--|

| Q | $x_2 x_1 = 00$ | $x_2 x_1 = 01$ | $x_2x_1=11$ | $x_2 x_1 = 10$ |  |  |

| 0 | 0/0            | 0/1            | 1/0         | 0/1            |  |  |

| 1 | 0/1            | 1/0            | 1/1         | 1/0            |  |  |

表 5-14 例 5-7 的编码状态表

(4) 求出电路的驱动方程和输出方程。表 5-14 中的  $x_2x_1$  和 Q 已经按格雷码排列,所以

如下.

& FF & 1D & CP

$$Q^{n+1} = x_2 x_1 + x_2 Q + x_1 Q$$

$$Y = x_1 \oplus x_2 \oplus Q$$

由于 D 触发器的特性方程为  $Q^{n+1}=D$ , 所以驱动方 程为

可将其看作卡诺图,通过化简得到状态方程和输出方程

$$D = x_2 x_1 + x_2 Q + x_1 Q$$

- 图 5-16 例 5-7 的逻辑电路图

- (5) 画出逻辑电路图,如图 5-16 所示。

- (6) 检查电路能否自启动。由电路的状态图 5-15 可知,电路中所有的状态都在有效序列 中,所以电路能够自启动。

【例 5-8】 用 JK 触发器和门电路设计一个 111 序 列检测器,以检测输入的信号序列是否为连续的111。

解:(1)根据例 5-3 的分析可知,该电路的输入变 量为x,输出变量为Y。原始状态表的建立可以按照 例 5-3 中介绍的方法,也可按照下面的方法建立。

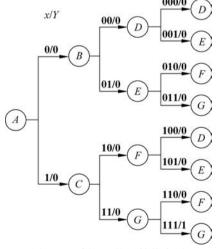

设该电路的初始状态为 A,根据题意列出电路在 不同x 序列输入下的状态变化规律及输出Y 的值,也 就是电路的原始状态图,如图 5-17 所示。

设电路的初始状态为A,若输入x=0,则电路进 入状态 B, 目输出 Y=0: 若输入 x=1, 则电路进入状 态 C,且输出  $Y=\mathbf{0}$ 。当电路进入状态 C 时,若  $x=\mathbf{0}$ , 则电路进入状态 F,且 Y=0; 若 x=1,则电路进入状 态 G,且输出  $Y=\mathbf{0}$ 。当电路进入 G 状态时,若  $x=\mathbf{0}$ ,

图 5-17 例 5-8 的原始状态图

则电路进入 F 状态,且 Y=0; 若 x=1,则电路进入状态 G,且输出 Y=1,因为此时输入的 x序列就是所要检测的序列 111。值得注意的是,在电路的状态为  $B \setminus C$  时,电路根据输入为 0或 1,分别转向状态  $D \setminus E \setminus F \setminus G$ 。由于检测序列 111 的长度为 3 位,因此电路只需要记忆前面 两个时刻的输入情况即可,这样,当第三个输入到达时,就可判断其结果是否为所要检测的序 列。因此,不需要再设新的状态。

根据图 5-17 可以建立该电路的原始状态表,如表 5-15 所示。

| $oldsymbol{S}$ | $S^{n+1}/Y$ |             |  |

|----------------|-------------|-------------|--|

| 3              | x = 0       | x=1         |  |

| A              | B/ <b>0</b> | C/ <b>0</b> |  |

| B              | D/ <b>0</b> | E/ <b>0</b> |  |

| C              | F/ <b>0</b> | G/ <b>0</b> |  |

| D              | D/ <b>0</b> | E/ <b>0</b> |  |

| E              | F/0         | G/ <b>0</b> |  |

| F              | D/ <b>0</b> | E/ <b>0</b> |  |

| G              | F/ <b>0</b> | G/1         |  |

表 5-15 例 5-8 的原始状态表

(2) 根据表 5-15 绘制如图 5-18 所示的隐含表。由隐含表可以得到全部等价对: $\{A,B\}$ 、  $\{A,D\}$ , $\{A,F\}$ , $\{B,D\}$ , $\{B,F\}$ , $\{C,E\}$ , $\{D,F\}$ 。最大等价类为 $\{A,B,D,F\}$ , $\{C,E\}$ , $\{G\}$ 。

令  $a = \{A, B, D, F\}, b = \{C, E\}, c = \{G\},$ 并将这种替代关系应用于表 5-15 所示的原始 状态表,便可得到最简状态表,如表 5-16 所示。可见,例 5-3 得出的状态表并非最简。

| S | $S^{n+1}/Y$ |             |  |

|---|-------------|-------------|--|

|   | x = 0       | x=1         |  |

| ā | a/0         | <i>b</i> /0 |  |

| b | a/0         | c/0         |  |

| С | a/0         | c/1         |  |

表 5-16 例 5-8 的最简状态表

| $Q_1Q$ | $Q_0$ |      |      |      |

|--------|-------|------|------|------|

| x      | 00    | 01   | 11   | 10   |

| 0      | 00/0  | 00/0 | ××/× | 00/0 |

| 1      | 01/0  | 10/0 | ××/× | 10/1 |

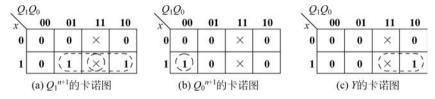

样确定的  $a \ b \ c \$  状态编码方案为: a = 00, b = 01, c = 10。 (4) 根据表 5-16 和状态编码方案画出电路的状态/输

图 5-19 例 5-8 的状态/输出卡诺图 出卡诺图(相当干编码状态表),如图 5-19 所示。

(3) 最简状态表中有 3 个状态, 应选用两个触发器。

根据编码规则,状态 a 和 b, a 和 c 一定要取相邻编码,这

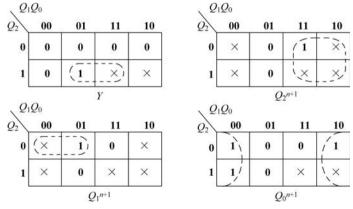

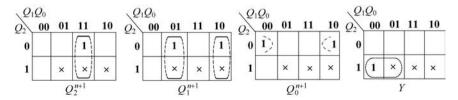

将图 5-19 所示卡诺图分解成  $Q_1^{n+1}$   $Q_2^{n+1}$  和输出 Y 的三个卡诺图, 如图 5-20(a)、 图 5-20(b)和图 5-20(c)所示,利用卡诺图可求得各触发器的状态方程和输出方程。

图 5-20 例 5-8 的卡诺图分解

由图 5-20 可得电路的状态方程、输出方程

$$Q_1^{n+1} = xQ_1 + xQ_0 = xQ_1 + xQ_0(Q_1 + \bar{Q}_1) = xQ_0\bar{Q}_1 + xQ_1$$

$$Q_0^{n+1} = x\bar{Q}_1\bar{Q}_0 = x\bar{Q}_1\bar{Q}_0 + \bar{\mathbf{1}} \cdot Q_0$$

$$Y = xQ_1$$

将状态方程与 JK 触发器的特性方程相比较,便可得到驱动方程

$$\begin{cases} J_1 = x Q_0 & K_1 = \bar{x} \\ J_0 = x \bar{Q}_1 & K_0 = \mathbf{1} \end{cases}$$

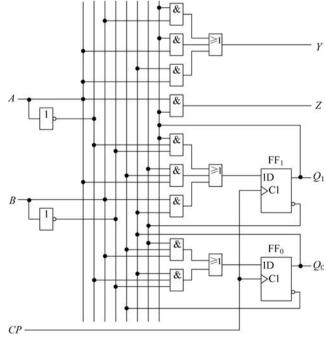

- (5) 根据驱动方程和输出方程可以画出本例的逻辑电路图,如图 5-21 所示。

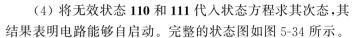

- (6) 电路的状态图如图 5-22 所示。由图可知,当电路进入无效状态 11 后,若 x=0,则电 路转入 00 状态; 若 x=1,则电路转入 10 状态。因此,所设计的电路能够自启动。

- 【例 5-9】 设计一个饮料自动售货机的逻辑电路。它的投币口每次只能投入一枚五角或 一元的硬币,投入一元五角硬币后机器自动给出一杯饮料,投入两元(两枚一元)硬币后,在给 出饮料的同时自动找回一枚五角的硬币。

图 5-21 例 5-8 的逻辑电路图

图 5-22 例 5-8 的状态图

**解**:(1)取投币信号为输入逻辑变量,投入一枚一元硬币时用A=1表示,未投入时用 A=0 表示;投入一枚五角硬币时用 B=1 表示,未投入时用 B=0 表示。给出饮料和找钱为 两个输出变量,分别以 $Y \setminus Z$ 表示,给出饮料时Y = 1,未给出时Y = 0;找回一枚五角硬币时

### Z=1,不找回时 Z=0。

假定通过传感器产生的投币信号(A=1)或 B=1)在电路转入新的状态时也随之消失,否 则将被误认为是再一次投币的信号。

设未投币前电路的初始状态为 S。,投入五角 硬币以后为 $S_1$ ,投入一元硬币(包括投入一枚一元 硬币或两枚五角硬币的情况)以后为 S<sub>2</sub>。再投入 一枚五角硬币后电路返回  $S_0$ ,同时输出为 Y=1、 Z=0; 如果投入的是一枚一元硬币,则电路也应返 回  $S_0$ ,同时输出为 Y=1、Z=1。根据以上分析,可 以画出如图 5-23 所示的原始状态图。

由图 5-23 可以列出原始状态表,如表 5-17 所示。

图 5-23 例 5-9 的原始状态图

|                            | $S^{n+1}/YZ$               |                |                    |         |  |  |

|----------------------------|----------------------------|----------------|--------------------|---------|--|--|

| S                          | AB = 00                    | AB = 01        | AB = 10            | AB = 11 |  |  |

| $S_{\scriptscriptstyle 0}$ | S <sub>0</sub> /00         | $S_1/00$       | $S_2/00$           | ×/××    |  |  |

| ${S}_1$                    | $S_1/00$                   | $S_{2}/00$     | S <sub>0</sub> /10 | ×/××    |  |  |

| $S_{2}$                    | S <sub>2</sub> / <b>00</b> | $S_{\circ}/10$ | $S_{\circ}/11$     | ×/××    |  |  |

表 5-17 例 5-19 的状态表

因为正常工作时不会出现 AB=11 的情况, 所以与之相关的项可以作为无关项处理。

- (2) 由表 5-17 可知,该状态表不能再化简,为最简状态表。

- (3) 根据以上分析可知,电路有三个状态,故选用两个触发器。设  $S_0 = 00$ 、 $S_1 = 01$ 、 $S_2 = 10$ , 代入表 5-17,即可得到编码状态表,如表 5-18 所示。

| 0.0      | $Q_1^{n+1}Q_0^{n+1}/YZ$ |         |         |         |  |  |  |

|----------|-------------------------|---------|---------|---------|--|--|--|

| $Q_1Q_0$ | AB = 00                 | AB = 01 | AB = 10 | AB = 11 |  |  |  |

| 00       | 00/00                   | 01/00   | 10/00   | ×/××    |  |  |  |

| 01       | 01/00                   | 10/00   | 00/10   | ×/××    |  |  |  |

| 10       | 10/00                   | 00/10   | 00/11   | ×/××    |  |  |  |

表 5-18 例 5-9 的编码状态表

| AB | 00    | 01    | 11    | 10    |

|----|-------|-------|-------|-------|

| 00 | 00/00 | 01/00 | ××/×× | 10/00 |

| 01 | 01/00 | 10/00 | ××/×× | 00/10 |

| 11 | ××/×× | ××/×× | ××/×× | ××/×× |

| 10 | 10/00 | 00/10 | ××/×× | 00/11 |

图 5-24 例 5-9 电路状态/输出卡诺图

(4) 因为设计要求中没有对触发器的选择做具 体规定,在本例中选用 D 触发器完成该时序电路设 计。根据表 5-18 可以画出电路的状态/输出卡诺图, 如图 5-24 所示。

将图 5-24 所示卡诺图分解成  $Q_1^{n+1}$  、 $Q_0^{n+1}$  、Y 和 Z四个卡诺图,如图 5-25(a)、(b)、(c)、(d)所示,利用卡 诺图可求得各触发器的状态方程和输出方程。

由图 5-25 可得电路的状态方程、输出方程

将状态方程与 D 触发器的特性方程相比较,便可得到驱动方程

$$D_1 = Q_1 \overline{A} \overline{B} + \overline{Q}_1 \overline{Q}_0 A + Q_0 B$$

$$D_{\scriptscriptstyle 0} = \bar{Q}_{\scriptscriptstyle 1} \bar{Q}_{\scriptscriptstyle 0} B + Q_{\scriptscriptstyle 0} \bar{A} \, \bar{B}$$

(5) 根据驱动方程和输出方程可画出本例的逻辑电路图,如图 5-26 所示。

图 5-26 例 5-9 的逻辑电路图

(6) 电路的状态图如图 5-27 所示。由图可知,当电路进入无效状态 11 后,在没有输入信 号的情况下(即 AB = 00 时)不能自行返回有效循环,所以不能自启动。当 AB = 01 或 AB=10 时,电路在时钟信号作用下,虽然能返回有效循环中,但收费结果是错误的。因此,在 开始工作时应将电路置为00状态。

图 5-27 例 5-9 的状态图

## \*5.4 异步时序电路

#### 异步时序电路的分析 5.4.1

异步时序电路的分析步骤和同步时序电路的分析步骤基本相同,但因为异步时序电路没 有统一的时钟信号来控制所有存储电路的状态变化,因此,分析时应特别注意状态变化与时钟 的——对应关系。下面举例来说明异步时序电路的分析方法。

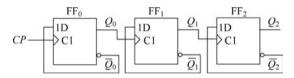

【例 5-10】 分析图 5-28 所示时序电路, 画出状态图和时序图。

图 5-28 例 5-10 的电路图

### 解:(1) 电路的时钟方程为

$$CP_2 = Q_1$$

,  $CP_1 = Q_0$ ,  $CP_0 = CP$

驱动方程为

$$D_2 = \bar{Q}_2$$

,  $D_1 = \bar{Q}_1$ ,  $D_0 = \bar{Q}_0$

### (2) 电路的状态方程为

$$Q_2^{n+1} = D_2 = \overline{Q}_2$$

, $CP_2$ (即  $Q_1$ )上升沿有效  $Q_1^{n+1} = D_1 = \overline{Q}_1$ , $CP_1$ (即  $Q_0$ )上升沿有效  $Q_0^{n+1} = D_0 = \overline{Q}_0$ , $CP_0$ (即  $CP$ )上升沿有效

(3) 根据状态方程列出时序电路的状态转换表,如表 5-19 所示。

| 表 5-19 | 例 5-10 | 的状态转换表 |

|--------|--------|--------|

|--------|--------|--------|

| Q 2 | $Q_1$ | $Q_0$ | $Q_2^{n+1}$ | $Q_1^{n+1}$ | $Q_0^{n+1}$ | CP <sub>2</sub> | CP <sub>1</sub> | CP <sub>0</sub> |

|-----|-------|-------|-------------|-------------|-------------|-----------------|-----------------|-----------------|

| 0   | 0     | 0     | 1           | 1           | 1           | <b>↑</b>        | <b>↑</b>        | <b>^</b>        |

| 0   | 0     | 1     | 0           | 0           | 0           | _               | ¥               | <b>^</b>        |

在根据状态方程计算时,还要依据各触发器的时钟方程来确定触发器的时钟脉冲信号是 否有效。如果有效,可按照状态方程计算出触发器的次态;如果无效,则触发器将保持原来的 状态不变。例如,当电路的现态为  $Q_0Q_1Q_0=010$  时,由状态方程计算出的电路次态为  $Q_0^{n+1}$  $Q_1^{n+1}Q_0^{n+1}=101$ 。如果 CP 出现一个上升沿,由时钟方程可知,CP。为上升沿,CP。有效,触 发器 FF。的状态  $Q_0$  由 0 变到 1;当  $Q_0$  由 0 变到 1 时, $CP_1$  为上升沿, $CP_1$  有效,触发器 FF\_1 的状态  $Q_1$  由 1 变到 0: 当  $Q_1$  由 1 变到 0 时, $CP_2$  为下降沿, $CP_2$  无效,触发器  $FF_2$  保持原状 态不变,即  $Q_0$  仍为 0。因此,电路的实际次态为  $Q_0^{n+1}Q_0^{n+1}=001$ 。

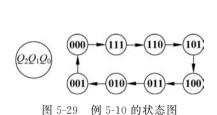

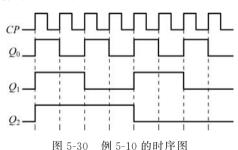

(4) 根据表 5-19 画出状态图和时序图,分别如图 5-29、图 5-30 所示。

#### 异步时序电路的设计 5.4.2

异步时序电路中各触发器状态的改变不是同时进行的,因而在设计异步时序电路时,要为 各个触发器选择合适的时钟脉冲信号。下面举例来说明异步时序电路的设计方法。

图 5-31 例 5-11 的状态图

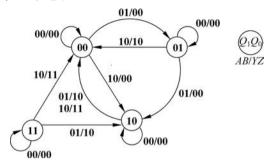

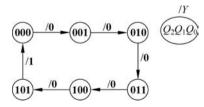

【例 5-11】 按图 5-31 的状态转换规律设计一个异步 时序电路。

解:(1)由如图 5-31 所示的状态图可知,本设计中状 态数目和编码方案是确定的,因此可略去状态化简和状态 编码两步。

电路具有六个状态,因此在设计中应选用三个触发

器,这里选用三个 CP 上升沿触发的 D 触发器来实现设计。根据状态图可以画出电路的时序图, 如图 5-32 所示。

(2) 根据状态图 5-31 可以得到状态转换表,如表 5-20 所示。

图 5-32 例 5-11 的时序图

表 5-20 例 5-11 的状态转换表

| Q 2 | $Q_1$ | $Q_0$ | $Q_2^{n+1}$ | $Q_1^{n+1}$ | $Q_0^{n+1}$ | Y | CP <sub>2</sub> | CP <sub>1</sub> | CP <sub>0</sub> |

|-----|-------|-------|-------------|-------------|-------------|---|-----------------|-----------------|-----------------|

| 0   | 0     | 0     | 0           | 0           | 1           | 0 | 0               | 0               | 1               |

| 0   | 0     | 1     | 0           | 1           | 0           | 0 | 0               | 1               | 1               |

| 0   | 1     | 0     | 0           | 1           | 1           | 0 | 0               | 0               | 1               |

| 0   | 1     | 1     | 1           | 0           | 0           | 0 | 1               | 1               | 1               |

| 1   | 0     | 0     | 1           | 0           | 1           | 0 | 0               | 0               | 1               |

| 1   | 0     | 1     | 0           | 0           | 0           | 1 | 1               | 0               | 1               |

(3) 要获得最简驱动方程,首先要为每个触发器选择适当的时钟脉冲。选择时钟脉冲的 基本原则是: 触发器需要翻转时,必须有时钟有效沿到达(CP=1),且触发沿越少越好。

从时序图 5-32 可知,每当电路状态变化,触发器 FF。都要翻转。因此,只有使用外部输入 时钟才能满足触发器  $FF_0$  的翻转要求,故触发器  $FF_0$  选用外部时钟信号  $CP_1$  选用  $CP_2$  $\bar{Q}_{0}$ 都可以,但依据触发沿最少的要求,应选择 $\bar{Q}_{0}$ ; FF。从 0 翻转到 1 时, $Q_{1}$  和  $\bar{Q}_{1}$  都无法满足 触发条件,因此  $CP_2$  只能选  $CP_3$  、 $\bar{Q}_0$  ,同样考虑触发沿最少,应选择  $\bar{Q}_0$  。根据以上分析,可以 得到电路的时钟方程为

$$CP_0 = CP$$

,  $CP_1 = \overline{Q}_0$ ,  $CP_2 = \overline{Q}_0$

根据表 5-20 画出电路输出信号和各触发器的次态卡诺图,如图 5-33 所示。

图 5-33 例 5-11 的卡诺图

画卡诺图时要注意的是,除了可将无效状态的最小项作为任意项处理外,在输入 CP 到来 后且电路状态变化时,不具备时钟条件的触发器的现态所对应的最小项,也可以当作任意项来

处理。本例中,因为 CP,和 CP。选用的是  $\overline{Q}$ 。,凡是  $\overline{Q}$ 。不变或由 1 变到 0 的最小项 000、010 、 100 也作为任意项处理。由卡诺图 5-33 可以求得电路的输出方程、状态方程

$$Y = Q_2 Q_0$$

$$Q_2^{n+1} = Q_1$$

$$Q_1^{n+1} = \bar{Q}_2 \bar{Q}_1$$

$$Q_0^{n+1} = \bar{Q}_0$$

将状态方程与 D 触发器的特性方程  $Q^{n+1} = D$  进行比较,可获得电路的驱动方程

$$D_2 = Q_1$$

$$D_1 = \bar{Q}_2 \bar{Q}_1$$

$$D_0 = \bar{Q}_0$$

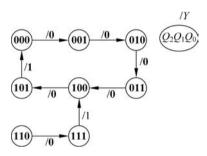

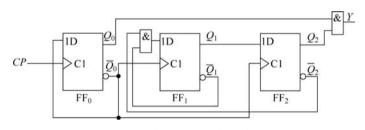

(5) 根据时钟方程、输出方程及驱动方程,可以画出 本例的逻辑电路图,如图 5-35 所示。

【提示】 在异步时序电路的设计中,时钟脉冲 CP 也 可以看作触发器的另一个输入端。

图 5-34 例 5-11 的完整状态图

图 5-35 例 5-11 的逻辑电路图

#### 5.5 常用时序逻辑电路

在实际工作中,最常用的时序逻辑电路是寄存器、计数器、顺序脉冲发生器等,它们与各种 组合电路一起可以构成逻辑功能极其复杂的数字系统。目前,人们根据需要设计了很多种类 的中规模集成时序电路定型产品,可以一片或多片扩展构成所需要的功能模块,应用于多种数 字装置中。下面主要介绍寄存器和计数器的结构、类型、特点及逻辑功能。

5.5.1 寄存器

寄存器是用来暂时存放一组二进制数码的逻辑电路,广泛应用于数字系统中。寄存器具 有清除数码、接收数码、存放数码和传送数码等功能,由具有存储功能的触发器和门电路组合 起来构成。因为一个触发器只能存储一位二进制数码,所以存储 N 位二进制数码的寄存器需 要用 N 个触发器组成。按逻辑功能的不同,寄存器可分为数码寄存器和移位寄存器。

#### 1. 数码寄存器

数码寄存器又称为基本寄存器或数据寄存器,只能并行送入数码,需要时也只能并行输 出。对数码寄存器中的触发器,只要求它具有置1、置0的功能即可,因此,不论是同步 RS 触 发器,还是主从结构或边沿触发的触发器,都可以构成数码寄存器。

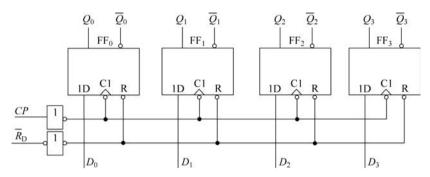

图 5-36 所示是由四个边沿 D 触发器组成的 4 位集成寄存器 74LS175 的逻辑电路图。其 中 $,\bar{R}_{\rm D}$  是异步复位端 $,D_{\rm S}\sim D_{\rm O}$  是并行数据输入端,CP 为时钟控制端 $,Q_{\rm S}\sim Q_{\rm O}$  是并行数据输 出端。

图 5-36 74LS175 的逻辑电路图

74LS175 的功能如表 5-21 所示。

| $\overline{R}_{D}$ | СР       | $D_3$ | D 2      | $D_1$    | $D_0$                      | $Q_3^{n+1}$ | $Q_2^{n+1}$ | $Q_1^{n+1}$ | $Q_0^{n+1}$                | 工作状态 |

|--------------------|----------|-------|----------|----------|----------------------------|-------------|-------------|-------------|----------------------------|------|

| 0                  | ×        | ×     | ×        | ×        | ×                          | 0           | 0           | 0           | 0                          | 异步复位 |

| 1                  | <b>↑</b> | $D_3$ | $D_2$    | $D_1$    | $D_{\scriptscriptstyle 0}$ | $D_3$       | $D_{2}$     | $D_1$       | $D_{\scriptscriptstyle 0}$ | 送数   |

| 1                  | 1        | ×     | ×        | $\times$ | $\times$                   | $Q_3$       | $Q_2$       | $Q_1$       | $Q_0$                      | 保持   |

| 1                  | 0        | ×     | $\times$ | $\times$ | $\times$                   | $Q_3$       | $Q_2$       | $Q_1$       | $oldsymbol{Q}_0$           | 保持   |

表 5-21 74LS175 的功能表

当 $\bar{R}_{\rm D}=0$ 时,寄存器异步复位。无论寄存器中原来的内容是什么,只要 $\bar{R}_{\rm D}=0$ ,就立即将 4个D触发器都复位到0状态。

当 $\bar{R}_{\mathrm{D}} = 1$  时,在CP 上升沿送数。无论寄存器中原来存储的数码是什么,当 $\bar{R}_{\mathrm{D}} = 1$  时,在 CP 上升沿到来时刻,加在并行输入端的数码  $D_3 \sim D_0$  马上被并行送入到寄存器中。寄存器 的输出数据可以并行从  $Q_3 \sim Q_0$  端引出,即  $Q_3^{n+1}Q_2^{n+1}Q_1^{n+1}Q_0^{n+1} = D_3D_2D_1D_0$ ,实现并行输 入、并行输出的功能。

当 $\bar{R}_{\rm D}=1$ ,CP 为上升沿以外的时间,寄存器内容保持不变,即各个输出端的状态与输入 无关。

### 2. 移位寄存器

移位寄存器不仅具有存储数码的功能,而且存储的数码还能在移位脉冲(时钟脉冲)的作 用下,依次向左或向右移动。因此,移位寄存器不但可以用来存储数码,还可以用来实现数据 的串行-并行转换、数值的运算及数据处理等。根据移位方式不同,移位寄存器可分为单向移 位寄存器和双向移位寄存器两类。

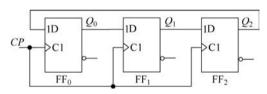

### 1) 单向移位寄存器

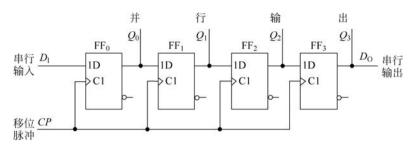

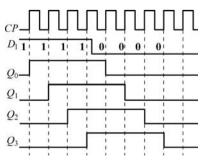

单向移位寄存器又分为左移移位寄存器和右移移位寄存器,图 5-37 所示是用四个边沿 D 触发器构成的 4 位右移移位寄存器。电路中  $D_1$  为外部串行输入端,在触发脉冲作用下将数 据依次移入寄存器;  $D_0$  为串行输出端;  $Q_0 \sim Q_0$  为并行输出端。

图 5-37 所示电路中各触发器的驱动方程为

用 D 触发器构成的 4 位右移移位寄存器 图 5-37

$$D_3 = Q_2$$

$D_2 = Q_1$

$D_1 = Q_0$

$D_0 = D_1$

$$(5-6)$$

将驱动方程式(5-6)代入 D 触发器的特性方程可得到状态方程

$$Q_{3}^{n+1} = Q_{2}$$

$Q_{2}^{n+1} = Q_{1}$

$Q_{1}^{n+1} = Q_{0}$

$Q_{0}^{n+1} = D_{1}$

$(5-7)$

通过状态方程式(5-7)可以看出,在CP脉冲作用下,外部串行输入 $D_1$ 移入 $Q_0,Q_0$ 移入  $Q_1,Q_1$  移入  $Q_2,Q_2$  移入  $Q_3$ ,总的效果相当于移位寄存器原有数据依次右移一位。根据状态 方程可列出如表 5-22 所示的状态转换表。

| $D_{\mathrm{I}}$ | СР       | $Q_0$ | $Q_1$ | $Q_2$ | $Q_3$ | $Q_0^{n+1}$ | $Q_1^{n+1}$ | $Q_2^{n+1}$ | $Q_3^{n+1}$ |

|------------------|----------|-------|-------|-------|-------|-------------|-------------|-------------|-------------|

| 1                | <b>↑</b> | 0     | 0     | 0     | 0     | 1           | 0           | 0           | 0           |

| 1                | <b>↑</b> | 1     | 0     | 0     | 0     | 1           | 1           | 0           | 0           |

| 1                | <b>↑</b> | 1     | 1     | 0     | 0     | 1           | 1           | 1           | 0           |

| 1                | <b>↑</b> | 1     | 1     | 1     | 0     | 1           | 1           | 1           | 1           |

| 0                | <b>↑</b> | 1     | 1     | 1     | 1     | 0           | 1           | 1           | 1           |

| 0                | <b>↑</b> | 0     | 1     | 1     | 1     | 0           | 0           | 1           | 1           |

| 0                | <b>↑</b> | 0     | 0     | 1     | 1     | 0           | 0           | 0           | 1           |

| 0                | <b>↑</b> | 0     | 0     | 0     | 1     | 0           | 0           | 0           | 0           |

表 5-22 4 位右移移位寄存器的状态转换表

图 5-38 4 位右移移位寄存器的时序图

从表 5-22 可看出, 当寄存器经过四个 CP 脉冲后, 依 次输入的 4 位数据全部移入了移位寄存器中,这种依次 输入数据的方式称为串行输入方式,每输入一个脉冲,数 据向右移动一位。若数据由  $Q_0 \sim Q_3$  同时输出,则为并 行输出方式; 若数据由 Q3 端逐次输出,则为串行输出方 式。图 5-38 是表 5-22 中串行输入情况下的时序图。

图 5-39 所示为 4 位左移移位寄存器,其工作原理与 右移移位寄存器无本质区别,只是连接相反,所以移位方 向变为由右向左。

图 5-39 用 D 触发器构成的 4 位左移移位寄存器

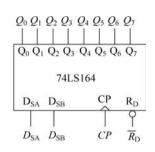

集成的单向移位寄存器产品很多,这里以比较典 型的 8 位单向移位寄存器 74LS164 为例,做简单介绍。

8位单向移位寄存器 74LS164 的简易图形符号如 图 5-40 所示。图中, D<sub>SA</sub>, D<sub>SB</sub> 为串行数据输入端, 实际使 用时把它们连接在一起,即  $D_s = D_{SA} \cdot D_{SB}$ ; CP 是移位 脉冲, 当CP 信号为上升沿时, 数据右移一位;  $\overline{R}_D$  是异步 复位输入端,低电平有效;  $Q_0 \sim Q_7$  是并行数据输出端,同 时 Q<sub>2</sub> 也是串行数据输出端。

图 5-40 74LS164 的简易图形符号

74LS164 的功能见表 5-23。

表 5-23 74LS164 的功能表

| $\overline{\overline{R}}_{\mathrm{D}}$ | $D_{SA} \cdot D_{SB}$ | СР       | $Q_0^{n+1}$ | $Q_1^{n+1}$                           | $Q_2^{n+1}$      | $Q_3^{n+1}$                | $Q_4^{n+1}$ | $Q_5^{n+1}$ | $Q_{6}^{n+1}$    | $Q_{7}^{n+1}$    | 工作状态   |

|----------------------------------------|-----------------------|----------|-------------|---------------------------------------|------------------|----------------------------|-------------|-------------|------------------|------------------|--------|

| 0                                      | ×                     | ×        | 0           | 0                                     | 0                | 0                          | 0           | 0           | 0                | 0                | 异步复位   |

| 1                                      | ×                     | 0        | $Q_0$       | $Q_1$                                 | $Q_2$            | $Q_{\scriptscriptstyle 3}$ | $Q_4$       | $Q_5$       | $oldsymbol{Q}_6$ | $Q_{7}$          | 保持     |

| 1                                      | 1                     | <b>↑</b> | 1           | $oldsymbol{Q}_{\scriptscriptstyle 0}$ | $oldsymbol{Q}_1$ | $Q_2$                      | $Q_3$       | $Q_4$       | $Q_5$            | $oldsymbol{Q}_6$ | 输入一个1  |

| 1                                      | 0                     | <b>↑</b> | 0           | $Q_{\scriptscriptstyle 0}$            | $oldsymbol{Q}_1$ | $Q_2$                      | $Q_3$       | $Q_4$       | $Q_5$            | $Q_6$            | 输入一个 0 |

由表 5-23 可知,74LS164 具有以下功能:

当 $\bar{R}_{\rm D}$ =**0**,74LS164 异步复位。

当 $\bar{R}_{D}$ =1,CP=0时,74LS164保持状态不变, $Q_{i}^{n+1}$ = $Q_{i}(i=0\sim7)$ 。

当 $\bar{R}_D = 1$ 、CP 的上升沿到来时,将加在  $D_S = D_{SA} \cdot D_{SB}$  端的二进制数码依次送入 74LS164 中。状态方程为

$$\begin{cases}

Q_0^{n+1} = D_{SA} \cdot D_{SB} \\

Q_1^{n+1} = Q_0 \\

Q_2^{n+1} = Q_1 \\

Q_3^{n+1} = Q_2

\end{cases}$$

$$Q_4^{n+1} = Q_3 \\

Q_5^{n+1} = Q_4 \\

Q_6^{n+1} = Q_5 \\

Q_7^{n+1} = Q_6

\end{cases}$$

(5-8)

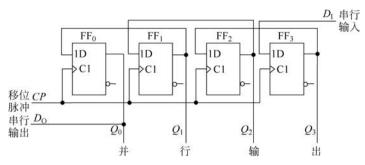

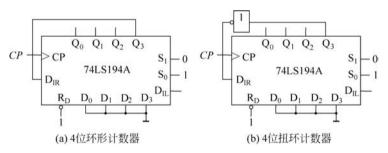

### 2) 双向移位寄存器

综合左移和右移移位寄存器电路,若增加移位方向控制信号和控制电路,就可以构成双向

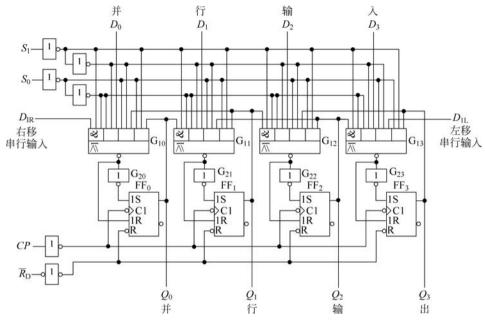

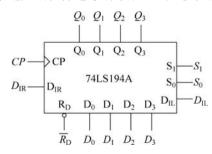

移位寄存器。为了方便扩展逻辑功能和增加使用的灵活性,在定型生产的移位寄存器集成电 路上还附加了异步复位、状态保持、数据并行输入和并行输出等功能。图 5-41 所示的 74LS194A 就是一个典型的 4 位双向移位寄存器。

图 5-41 74LS194A 的逻辑电路图

74LS194A由四个触发器FF<sub>0</sub>、FF<sub>1</sub>、FF<sub>2</sub>、FF<sub>3</sub>和各自的输入控制电路组成。图中的D<sub>IR</sub> 为数据右移串行输入端; $D_{\parallel}$ 为数据左移串行输入端; $D_{0} \sim D_{0}$ 为数据并行输入端; $Q_{0} \sim Q_{0}$ 为数据的并行输出端;移位寄存器的工作状态由控制端  $S_0$  和  $S_1$  的状态指定;  $\overline{R}_0$  是异步复 位输入端,低电平有效; CP 是移位脉冲。74LS194A 的简易图形符号如图 5-42 所示。

图 5-42 74LS194A 的简易图形符号

图 5-41 中,当  $\bar{R}_D = \mathbf{0}$  时,所有触发器将同时复位, 而且复位操作不受其他输入端状态的影响;只有当 $\bar{R}_{\rm D}$ =1时,74LS194A才能正常工作。现以第二位触发器  $FF_1$  为例,分析一下当 $\overline{R}_D = 1, S_0, S_1$  取不同值时移位寄 存器的工作状态。由图 5-41 可知,FF, 的输入控制电路 是由"与或非"门 G11 和反相器 G21 组成的一个具有互补 输出的 4 选 1 数据选择器。它的互补输出作为 FF。的 输入信号。

当 $S_1 = S_0 = 0$  时, $G_1$ , 最右边的输入信号  $Q_1$  被选中,使触发器 FF<sub>1</sub> 的输入为  $S = Q_1$ ,  $R = \overline{Q}_1$ 。所以当 CP 上升沿到达时,  $FF_1$  被置成  $Q_1^{n+1} = Q_1$ 。此时寄存器工作在保持状态。

当  $S_1 = 1, S_0 = 0$  时, $G_1$  右边第二个输入信号  $Q_2$  被选中,使触发器  $FF_1$  的输入为  $S = Q_2$ ,  $R = \overline{Q}_2$ ,所以当 CP 上升沿到达时,FF<sub>1</sub> 被置成  $Q_1^{n+1} = Q_2$ 。此时寄存器工作在左移状态。

当  $S_1=\mathbf{0}$ , $S_0=\mathbf{1}$  时, $G_{11}$  最左边的输入信号  $Q_0$  被选中,使触发器  $\operatorname{FF}_1$  的输入为  $S=Q_0$ ,R= $\bar{Q}_{0}$ ,所以当 CP 上升沿到达时,FF, 被置成  $Q_{1}^{r+1}=Q_{0}$ 。此时寄存器工作在右移状态。

当  $S_1 = S_0 = 1$  时, $G_{11}$  左边第二个输入信号  $D_1$  被选中,使触发器  $\mathsf{FF}_1$  的输入为  $S = D_1$ ,R = 1

$\bar{D}_1$ ,所以当 CP 上升沿到达时, $FF_1$  被置成  $Q_1^{n+1} = D_1$ 。此时寄存器处于并行输入状态。

其他三个触发器的工作原理与 FF, 基本相同,这里不再赘述。根据以上分析,可以列出 4 位双向移位寄存器 74LS194A 的功能表,如表 5-24 所示。

| $\overline{R}_{D}$ | $S_1$ | $S_0$ | 工作状态           |

|--------------------|-------|-------|----------------|

| 0                  | ×     | ×     | 异步复位           |

| 1                  | 0     | 0     | 保持<br>右移<br>左移 |

| 1                  | 0     | 1     | 右移             |

| 1                  | 1     | 0     | 左移             |

| 1                  | 1     | 1     | 并行输入           |

表 5-24 74LS194A 的功能表

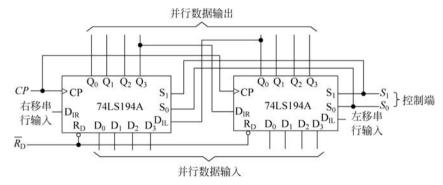

当一片移位寄存器的位数不够用时,可使用多片移位寄存器进行扩展。图 5-43 所示是用 两片 74LS194A 扩展成的 8 位双向移位寄存器的连接图。只需将两片 74LS194A 的 CP  $\overline{R}_D$  $S_0$ 、 $S_1$  分别并联,再将一片的  $Q_0$  接至另一片的  $D_{IR}$  端,而另一片的  $Q_0$  接到这一片的  $D_{IR}$  端 即可。

图 5-43 两片 74LS194A 扩展成的 8 位双向移位寄存器

#### 计数器 5.5.2

数字系统中,把记忆输入时钟脉冲个数的操作称为计数,能实现计数操作的电路称为计数 器。计数器所能记忆的最大脉冲个数称为计数器的模(计数容量)。除了用于对脉冲的计数 外,计数器还可以用于分频、定时、数字运算、产生节拍脉冲和脉冲序列等。

计数器的种类很多,按时钟控制方式的不同可分为异步计数器和同步计数器,按计数器 中数字编码方式的不同可分为二进制计数器、非二进制计数器; 按计数器计数容量的不同可 分为十进制计数器、十三进制计数器、四十进制计数器等;按计数过程中数值增减的不同可分 为加法计数器、减法计数器和可逆计数器。

### 1. 同步二进制计数器

当输入计数脉冲到来时,按二进制规律进行计数的电路称为二进制计数器。

1) 同步二进制加法计数器

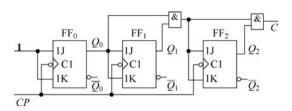

图 5-44 所示是由三个 JK 触发器构成的 3 位同步二进制加法计数器的逻辑电路图。电路 中三个 JK 触发器各自的输入端 J 、K 连接在一起构成了 T 触发器应用模式,因此也可以看成 三个 T 触发器构成的 3 位同步二进制加法计数器。图中,CP 是计数脉冲输入端,C 为进位信 号输出端。

微课视版

图 5-44 3 位同步二进制加法计数器

由图 5-44 可见,各触发器的驱动方程为

$$J_0 = K_0 = 1$$

$J_1 = K_1 = Q_0$

$J_2 = K_2 = Q_1 Q_0$

电路的输出方程为

$$C = Q_2 Q_1 Q_0$$

将驱动方程代入JK触发器的特性方程得到电路的状态方程

$$Q_0^{n+1} = \overline{Q}_0$$

$Q_1^{n+1} = Q_1 \oplus Q_0$

$Q_2^{n+1} = Q_2 \oplus Q_1Q_0$

表 5-25 是电路的状态转换表。由表 5-25 可知,每来一个计数脉冲,计数器就加一个 1。随着输入计数脉冲个数的增加,计数器中的数值也增大,当计数器记满,即  $Q_2Q_1Q_0=111$  时,再来一个计数脉冲,计数器归零的同时给高位进位,即 C=1。

| 计数脉冲     |     | 进位输出  |       |   |

|----------|-----|-------|-------|---|

| 11 数 脉 冲 | Q 2 | $Q_1$ | $Q_0$ | C |

| 0        | 0   | 0     | 0     | 0 |

| 1        | 0   | 0     | 1     | 0 |

| 2        | 0   | 1     | 0     | 0 |

| 3        | 0   | 1     | 1     | 0 |

| 4        | 1   | 0     | 0     | 0 |

| 5        | 1   | 0     | 1     | 0 |

| 6        | 1   | 1     | 0     | 0 |

| 7        | 1   | 1     | 1     | 1 |

| 8        | 0   | 0     | 0     | 0 |

表 5-25 图 5-44 的状态转换表

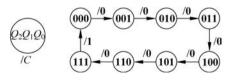

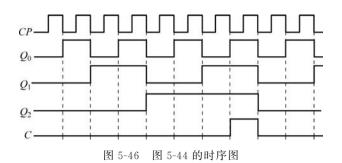

图 5-45 和图 5-46 分别是电路的状态图和时序图。

图 5-45 图 5-44 的状态图

由状态图可以看出,二进制计数器是一个满足模 $M=2^n$ 的计数器,其中n是触发器的个数。又因为每输入M个计数脉冲,计数器工作一个循环,并在输出端产生一个进位脉冲,所以二进制计数器也可称为M进制计数器或模M计数器。

由图 5-46 可以看出,若计数输入脉冲的频率为  $f_0$ ,则  $Q_0$ 、 $Q_1$ 、 $Q_2$  端输出脉冲的频率依次为  $\frac{1}{2}f_0$ , $\frac{1}{4}f_0$ , $\frac{1}{8}f_0$ 。针对计数器的这种分频功能,也将计数器称为分频器。

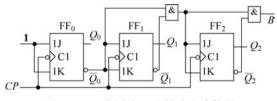

### 2) 同步二进制减法计数器

图 5-47 所示是由三个 JK 触发器构成的 3 位同步二进制减法计数器的逻辑电路图。同样,也可以由三个 T 触发器构成。图中, CP 是计数脉冲输入端, B 为借位信号输出端。

图 5-47 3 位同步二进制减法计数器

由图 5-47 可见,各触发器的驱动方程为

$$J_{0} = K_{0} = 1$$

$J_{1} = K_{1} = \overline{Q}_{0}$

$J_{2} = K_{2} = \overline{Q}_{1}\overline{Q}_{0}$

电路的输出方程为

$$B = \bar{Q}_2 \bar{Q}_1 \bar{Q}_0$$

电路的状态方程为

$$egin{aligned} Q_0^{\,n+1} &= & \, \overline{Q}_0 \ Q_1^{\,n+1} &= & \, Q_1 \, \oplus \, \overline{Q}_0 \ Q_2^{\,n+1} &= & \, Q_2 \, \oplus \, \overline{Q}_1 \overline{Q}_0 \end{aligned}$$

表 5-26 是电路的状态转换表。由表 5-26 可知,每输入一个计数脉冲,计数器减一个 1,当 不够减时向高位借位,显然向高位借来的 1 应当作 8,8-1=7。因此在表 5-26 中,当状态为 000 时,输入一个计数脉冲,不够减,向高位借 1 当作 8,减 1 后剩 7,计数器的状态由 000 转向 111,同时向高位送出借位信号,即 B=1。

图 5-48 是电路的状态图。

表 5-26 图 5-47 的状态转换表

| 计数脉冲    |     | 借位输出  |       |   |

|---------|-----|-------|-------|---|

| 11 致加小中 | Q 2 | $Q_1$ | $Q_0$ | В |

| 0       | 0   | 0     | 0     | 1 |

| 1       | 1   | 1     | 1     | 0 |

| 2       | 1   | 1     | 0     | 0 |

| 3       | 1   | 0     | 1     | 0 |

| 计数脉冲        |       | 电路状态  |         |   |  |  |

|-------------|-------|-------|---------|---|--|--|

| 71 发入 7小 7中 | $Q_2$ | $Q_1$ | $Q_{0}$ | В |  |  |

| 4           | 1     | 0     | 0       | 0 |  |  |

| 5           | 0     | 1     | 1       | 0 |  |  |

| 6           | 0     | 1     | 0       | 0 |  |  |

| 7           | 0     | 0     | 1       | 0 |  |  |

| 8           | 0     | 0     | 0       | 1 |  |  |

### 3) 同步二进制可逆计数器

除加法计数和减法计数方式外,还可引入控制信号,实现加/减(可逆)计数或可控计数。 5.2.2 节中的例 5-2 电路就是二进制可逆计数器。由例 5-2 的状态图(即图 5-8)可见,当外部 输入的控制信号 x=0 时,每来 4 个时钟脉冲,电路的状态按  $00 \rightarrow 01 \rightarrow 10 \rightarrow 11 \rightarrow 00$  规律变化, 当状态从11向00转换时,在输出端产生一个进位脉冲信号。可见,此时电路实现模4加法计 数器的功能。当 x=1 时,每来 4 个时钟脉冲,电路的状态按 00→11→10→01→00 规律变化, 当状态从11向10转换时,在输出端产生一个借位脉冲信号。可见,此时电路实现模4减法计 数器的功能。

所以,例 5-2 电路是一个 2 位同步二进制可逆计数器。x 为加/减控制信号,Y 为进位/借 位输出。电路的时序图如图 5-49 所示。

【例 5-12】 用 D 触发器和门电路设计一个 2 位同步二进制可控计数器,当控制信号x=0时,按自然二进制数加法计数; 当控制信号 x=1 时,按格雷码加法计数。

解:(1)设Y为进位信号,建立如表 5-27 所示的状态转换表。

图 5-48 图 5-47 的状态图

图 5-49 例 5-2 的时序图

表 5-27 例 5-12 的状态转换表

| x | $Q_1$ | $Q_{0}$ | $Q_1^{n+1}$ | $Q_0^{n+1}$ | Y |

|---|-------|---------|-------------|-------------|---|

| 0 | 0     | 0       | 0           | 1           | 0 |

| 0 | 0     | 1       | 1           | 0           | 0 |

| 0 | 1     | 0       | 1           | 1           | 0 |

| 0 | 1     | 1       | 0           | 0           | 1 |

| 1 | 0     | 0       | 0           | 1           | 0 |

| 1 | 0     | 1       | 1           | 1           | 0 |

| 1 | 1     | 0       | 0           | 0           | 1 |

| 1 | 1     | 1       | 1           | 0           | 0 |

(2) 由状态转换表抽象电路的状态方程和输出方程,进而得到驱动方程。

$$\begin{aligned} Q_1^{n+1} &= \sum (1,2,5,7) = xQ_0 + \bar{Q}_1Q_0 + \bar{x}Q_1\bar{Q}_0 = \overline{\bar{x}Q_1}Q_0 + \bar{x}Q_1\bar{Q}_0 = \bar{x}Q_1 \oplus Q_0 = D_1 \\ Q_0^{n+1} &= \sum (0,2,4,5) = x\bar{Q}_1 + \bar{x}\bar{Q}_0 = D_0 \\ Y &= \sum (3,6) = xQ_1\bar{Q}_0 + \bar{x}Q_1Q_0 = (x \oplus Q_0)Q_1 \end{aligned}$$

(3) 由驱动方程和输出方程画逻辑图,如图 5-50 所示。

图 5-50 例 5-12 的逻辑图

- 4) 集成同步二进制计数器

- (1) 同步二进制加法计数器。

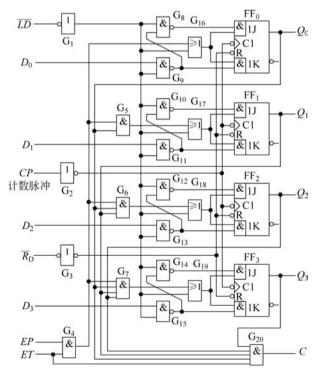

图 5-51 为集成 4 位同步二进制加法计数器 74161 的逻辑电路图。电路除了具有二进制 加法计数功能外,还具有预置数、保持和异步复位等功能。

图 5-51 74161 的逻辑电路图

74161 由四个 IK 触发器和一些控制电路组成。图中  $\overline{LD}$  为预置数控制端, $D_0 \sim D_0$  为数 据输入端,C 为进位输出端, $\overline{R}_{D}$  为异步复位端,EP 和ET 为工作状态控制端。74161 的简易 图形符号如图 5-52 所示。

图 5-52 74161 的简易图形符号

$Q_3Q_2Q_1Q_0 = D_3D_2D_1D_0$ .

由图 5-51 可见, 当  $\bar{R}_{\rm D}$ =**0** 时, 所有触发器将同时复位, 而且复位操作不受其他输入端状态的影响。

当 $\bar{R}_{\rm D}=1, \overline{LD}=0$ 时,电路工作在预置数状态。这时  $G_{16} \sim G_{10}$  门的输出始终是 1。所以触发器  $FF_{0} \sim FF_{0}$  输入 端  $J \setminus K$  的状态由  $D_0 \sim D_3$  的状态决定。当 CP 上升沿到 达时, 预置数  $D_0 \sim D_3$  被送到输出端  $Q_0 \sim Q_3$ , 使

当 $\overline{R}_D = \overline{LD} = 1$ , EP = 0, ET = 1 时, 由于这时  $G_{16} \sim G_{19}$  门的输出均为 0, 即触发器  $FF_0 \sim FF_3$  均处在 J = K = 0 的状态,因此 CP 信号到达时计数器的状态保持不变,同时 C 的 状态也保持不变。如果 ET=0,则 EP 无论为何状态,计数器状态均保持不变,但 C=0。

当 $\overline{R}_{D} = LD = ET = EP = 1$  时,电路处于计数状态,从 0000 状态开始计数,当连续输入 16 个计数脉冲后,电路将从 1111 状态返回 0000 状态, C 端从 1 跳变到 0。可以利用 C 端输出 的高电平或下降沿作为进位输出信号。

74161 的功能表如表 5-28 所示。

| СР       | $\overline{R}_{D}$ | LD | EP | ET | 工作状态               |

|----------|--------------------|----|----|----|--------------------|

| ×        | 0                  | ×  | ×  | ×  | 异步复位               |

| <b>↑</b> | 1                  | 0  | ×  | ×  | 预置数                |

| ×        | 1                  | 1  | 0  | 1  | 保持                 |

| ×        | 1                  | 1  | ×  | 0  | 保持(但 C= <b>0</b> ) |

|          | 1                  | 1  | 1  | 1  | 模 16 计数            |

表 5-28 74161 的功能表

74LS161 在内部电路结构上与 74161 有些区别,但外部引线配置、引脚排列及功能表与 74161相同。

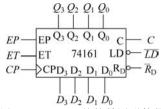

74LS163 也是 4 位同步二进制加法计数器,除了采用同步复位外,其余的功能与 74LS161 完全相同。图 5-53 是 74LS163 的简易图形符号,其功能如表 5-29 所示。

|          |    | •  |                 |                   |           |

|----------|----|----|-----------------|-------------------|-----------|

| СР       | CR | LD | CT <sub>P</sub> | $CT_{\mathrm{T}}$ | 工作状态      |

| <u> </u> | 0  | ×  | ×               | ×                 | 同步复位      |

| <b>↑</b> | 1  | 0  | ×               | ×                 | 预置数       |

| ×        | 1  | 1  | 0               | 1                 | 保持        |

| ×        | 1  | 1  | ×               | 0                 | 保持(但 C=0) |

| <b>↑</b> | 1  | 1  | 1               | 1                 | 模 16 计数   |

表 5-29 74LS163 的功能表

(2) 同步二进制可逆计数器。

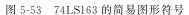

如图 5-54 所示为 4 位同步二进制可逆计数器 74LS191 的简易图形符号,功能表如表 5-30 所 示。这里省略了 74LS191 内部逻辑电路图,仅对其外部功能进行介绍。

图 5-54 74LS191 的简易图形符号

表 5-30 74LS191 的功能表

| CP <sub>1</sub> | $ar{oldsymbol{s}}$ | <del>LD</del> | $\overline{ar{U}}/ar{D}$ | 工作状态      |

|-----------------|--------------------|---------------|--------------------------|-----------|

| ×               | 1                  | 1             | ×                        | 保持        |

| ×               | ×                  | 0             | ×                        | 预置数       |

| <b>↑</b>        | 0                  | 1             | 0                        | 模 16 加法计数 |

|                 | 0                  | 1             | 1                        | 模 16 减法计数 |

$\overline{U}/D$  是加减控制端,当  $\overline{U}/D=\mathbf{0}$  时,74LS191 做加法计数;当  $\overline{U}/D=\mathbf{1}$  时,74LS191 做减法计数。

$\overline{LD}$  为预置数控制端,当  $\overline{LD}$  =  $\mathbf{0}$  时 74LS191 处于预置数状态, $D_0 \sim D_3$  被送入计数器中, 而不受时钟输入信号  $CP_1$  的控制。因此,74LS191 是异步预置数。

$\bar{S}$  是使能控制端,当  $\bar{S}=1$  时,74LS191 处于保持状态。

C/B 是进位、借位输出端,也称为最大值/最小值输出端。当计数器做加法计数且  $Q_3Q_2Q_1Q_0=1111$  时,C/B=1,有进位输出;当计数器做减法计数且  $Q_3Q_2Q_1Q_0=0000$  时, C/B=1,有借位输出。

$\overline{CP}_0$  是串行时钟输出端,当 C/B=1 时,在下一个  $CP_1$  上升沿到达前, $\overline{CP}_0$  端有一个负脉冲输出。  $Q_3$   $Q_2$   $Q_1$   $Q_0$

74LS191 只有一个时钟信号的输入端  $CP_1$ ,由  $\overline{U}/D$  电平决定 74LS191 做加法/减法计数,所以这种计数器 称为单时钟同步可逆计数器。

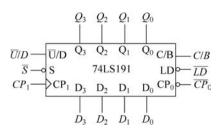

如果加法计数脉冲和减法计数脉冲来自两个不同的脉冲源,则为双时钟可逆计数器,74LS193 是常见的双时钟同步二进制可逆计数器,它的简易图形符号如图 5-55

图 5-55 74LS193 的简易图形符号

所示,功能表如表 5-31 所示。其中  $CP_{\, \mathrm{U}}$  是加法计数时钟脉冲输入端, $CP_{\, \mathrm{D}}$  是减法计数时钟脉冲输入端。

表 5-31 74LS193 的功能表

| <i>CP</i> <sub>U</sub> | CP <sub>D</sub> | $R_{\mathrm{D}}$ | LD | 工作状态      |

|------------------------|-----------------|------------------|----|-----------|

| ×                      | ×               | 1                | ×  | 异步复位      |

| ×                      | ×               | 0                | 0  | 预置数       |

| <b>↑</b>               | 1               | 0                | 1  | 模 16 加法计数 |

| 1                      | <b>↑</b>        | 0                | 1  | 模 16 减法计数 |

$R_{\rm D} = 1$  时,74LS193 异步复位。

$\overline{LD}$  为预置数控制端,当  $R_D = \mathbf{0}$ ,  $\overline{LD} = \mathbf{0}$  时 74LS193 处于预置数状态, $D_0 \sim D_3$  被送入计数器中,与时钟信号 CP 无关。因此,74LS193 是异步预置数。

当 $R_D$ =**0**, $CP_D$ =**1**时,74LS193 做加法计数。当加法计数达到最大值,且下一个 $CP_U$  的上升沿到来时,该计数器返回**0000**,同时进位信号输出端 $\overline{CO}$  输出一个进位脉冲。

当 $R_D$ =**0**, $CP_U$ =**1** 时,74LS193 做减法计数,当减法计数达到 **0000**,且下一个  $CP_D$  的上升沿到来时,该计数器返回 **1111**,同时借位信号输出端  $\overline{BO}$  输出一个借位脉冲。

### 2. 同步非二进制计数器

除二进制计数器以外的计数器称为非二进制计数器。显然,非二进制计数器不满足*M*=2"关系。这里主要介绍十进制计数器、环形及扭环计数器及其他进制计数器。

### 1) 十讲制计数器

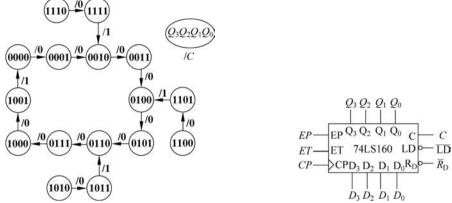

十进制计数器是在二进制计数器的基础上得到的,也称为二-十进制计数器。最常见的十进制计数器是 8421BCD 十进制计数器。图 5-56 所示电路是由四个 JK 触发器构成的一种同步 8421BCD 十进制计数器的逻辑电路图。

图 5-56 十进制计数器逻辑电路图

由图 5-56 可见,各触发器的驱动方程为

$$J_{0} = K_{0} = 1$$

$J_{1} = K_{1} = Q_{0} \bar{Q}_{3}$

$J_{2} = K_{2} = Q_{1} Q_{0}$

$J_{3} = K_{3} = Q_{2} Q_{1} Q_{0} + Q_{3} Q_{0}$

电路的输出方程为

$$C = Q_3 Q_0$$

电路的状态方程为

$$egin{aligned} Q_0^{n+1} &= ar{Q}_0 \ Q_1^{n+1} &= ar{Q}_3 Q_0 \oplus Q_1 \ Q_2^{n+1} &= Q_1 Q_0 \oplus Q_2 \ Q_3^{n+1} &= (Q_2 Q_1 Q_0 + Q_3 Q_0) \oplus Q_3 \end{aligned}$$

根据状态方程和输出方程可得该计数器的状态图,如图 5-57 所示。

由图 5-57 可见,计数器最初处于初始状态 **0000**,当第一个计数脉冲到来时,计数器加 **1**,进入 **0001** 状态,以此类推,当第九个计数脉冲到来时,进入 **1001** 状态,当第十个计数脉冲到来时,计数器回到初始状态 **0000**,同时产生 1 个进位脉冲,即逢十进一。

74LS160 是一个 8421BCD 同步十进制计数器。其引脚结构与前面介绍的 74161 相同,区别在于当 $\bar{R}_{\rm D} = \overline{LD} = ET = EP = 1$  时,74LS160 按十进制规律计数,从 **0000** 到 **1001**,当电路

处于 **1001** 状态时,进位端 C=1。74LS160 的简易图形符号如图 5-58 所示,其功能表如 表 5-32 所示。

图 5-57 图 5-56 的状态图

图 5-58 74LS160 的简易图形符号

表 5-32 74LS160 的功能表

| CP       | $\overline{R}_{D}$ | LD | EP | ET | 工作状态               |

|----------|--------------------|----|----|----|--------------------|

| ×        | 0                  | ×  | ×  | ×  | 异步复位               |

| <b>↑</b> | 1                  | 0  | ×  | ×  | 预置数                |

| ×        | 1                  | 1  | 0  | 1  | 保持                 |

| ×        | 1                  | 1  | ×  | 0  | 保持(但 C= <b>0</b> ) |

| <b>↑</b> | 1                  | 1  | 1  | 1  | 模 10 计数            |

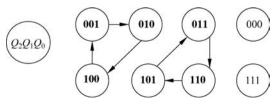

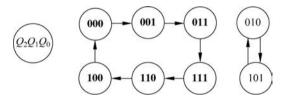

### 2) 环形计数器及扭环计数器

移位寄存器可以构成环形计数器及扭环计数器。如图 5-59 所示电路,只要将 3 位移位寄 存器首尾相接,即可构成3位环形计数器。

图 5-59 3 位环形计数器逻辑图

由图 5-59 可以列出电路的状态方程为

$$Q_2^{n+1} = D_2 = Q_1$$

$$Q_1^{n+1} = D_1 = Q_0$$

$$Q_0^{n+1} = D_0 = Q_2$$

省略状态转换表,根据状态方程直接画出状态图,如图 5-60 所示。

图 5-60 图 5-59 的状态图

由状态图可知,电路的8个状态存在多个循环,若洗001→010→100为有效循环,则其他 循环为无效循环。可见,图 5-59 所示电路是不能自启动的模 3 计数器,若要使电路具有自启 动功能,可通过修改逻辑设计来实现。

环形计数器结构简单,工作可靠且速度较高,在现代数字系统中有较广泛的应用。但其状 态利用率较低,由 n 位移位寄存器构成的环形计数器只有 n 个有效状态。

若改变环形计数器的接法,如图 5-61 所示,则电路构成 3 位扭环计数器。

图 5-61 3 位扭环计数器逻辑图

按着同样的分析方法,可画出3位扭环计数器的状态图,如图5-62所示。

图 5-62 图 5-61 的状态图

由状态图可知,电路的 8 个状态存在 2 个循环,若选 000→001→011→111→110→100 为 有效循环,则图 5-61 电路是不能自启动的模 6 格雷码计数器。

与环形计数器相比,n 位移位寄存器构成的扭环计数器有 2n 个有效状态,这提高了状态 利用率。在实际应用中,可利用集成移位寄存器实现环形计数器和扭环计数器,图 5-63 所示 电路是用集成移位寄存器 74LS194 构成的 4 位环形计数器和 4 位扭环计数器。

图 5-63 74LS194 构成的计数器

除上面介绍的非二进制计数器外,工程应用中还经常需要很多其他模数的计数器,这类计 数器的状态中或多或少存在无效状态,下面举例说明由触发器构成的这类计数器的分析和设 计方法。

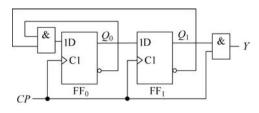

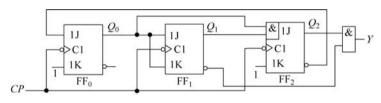

【例 5-13】 分析如图 5-64 所示时序电路的逻辑功能。

解:(1) 写出输出方程和驱动方程。

$$Y = Q_1 \cdot CP$$

$$\begin{cases} D_1 = Q_0 \\ D_0 = \overline{Q}_1 \overline{Q}_0 \end{cases}$$

图 5-64 例 5-13 的时序图

(2) 求出状态方程。

$$\begin{cases} Q_1^{n+1} = D_1 = Q_0 \\ Q_0^{n+1} = D_0 = \overline{Q}_1 \overline{Q}_0 \end{cases}$$

(3) 列出状态转换表,如表 5-33 所示,画出状态图如图 5-65 所示。

表 5-33 例 5-13 的状态转换表

| $Q_1$ | $Q_{0}$ | $Q_1^{n+1}$ | $Q_0^{n+1}$ | Y |

|-------|---------|-------------|-------------|---|

| 0     | 0       | 0           | 1           | 0 |

| 0     | 1       | 1           | 0           | 0 |

| 1     | 0       | 0           | 0           | 1 |

| 1     | 1       | 1           | 0           | 1 |

(4) 由状态图可知,该电路是能够自启动的同步模 3 加法 计数器。

【例 5-14】 用 JK 触发器和门电路设计一个同步模 5 加法 计数器。

图 5-65 例 5-13 的状态图

解:(1)建立状态转换表,如表 5-34 所示。

表 5-34 例 5-14 的状态转换表

| $Q_2$ | $Q_2$ | $Q_0$ | $Q_2^{n+1}$ | $Q_1^{n+1}$ | $Q_0^{n+1}$ | Y |

|-------|-------|-------|-------------|-------------|-------------|---|

| 0     | 0     | 0     | 0           | 0           | 1           | 0 |

| 0     | 0     | 1     | 0           | 1           | 0           | 0 |

| 0     | 1     | 0     | 0           | 1           | 1           | 0 |

| 0     | 1     | 1     | 1           | 0           | 0           | 0 |

| 1     | 0     | 0     | 0           | 0           | 0           | 1 |

| 1     | 0     | 1     | x           | x           | x           | x |

| 1     | 1     | 0     | x           | x           | x           | x |

| 1     | 1     | 1     | x           | x           | x           | x |

(2) 利用卡诺图化简状态方程和输出方程,见图 5-66。

图 5-66 例 5-14 的状态方程和输出方程卡诺图

状态方程和输出方程为

$$egin{aligned} Q_2^{n+1} = & Q_1 Q_0 = Q_1 Q_0 ar{Q}_2 + Q_1 Q_0 Q_2 = Q_1 Q_0 ar{Q}_2 \ Q_1^{n+1} = & Q_0 ar{Q}_1 + ar{Q}_0 Q_1 \ Q_0^{n+1} = & ar{Q}_2 ar{Q}_0 \ Y = & Q_2 ar{Q}_1 \end{aligned}$$

(3) 结合 JK 触发器的特性方程确定驱动方程。

$$J_2 = Q_1 Q_0$$

$K_2 = 1$

$J_1 = Q_0$   $K_1 = Q_0$

$J_0 = \bar{Q}_2$   $K_0 = 1$

(4) 画逻辑图如图 5-67 所示。

图 5-67 例 5-14 的逻辑图

### 3. 异步计数器

异步计数器中各触发器的时钟信号不再统一输入计数脉冲,有的触发器的时钟信号是其他触发器的输出,各触发器输出状态的更新要视有无自己的时钟信号而定。与同步计数器相比,异步计数器的电路构成简单,但计数速度低。

通过对例 5-10 中电路的分析可知,其状态图中的 8 个状态按递减规律循环变化,是一个摩尔型的 3 位二进制异步减法计数器。从例 5-11 设计的时序电路的状态图可以看出,电路是一个异步模 6 加法计数器。其他类型和模数的异步计数器的分析和设计方法这里不再赘述,读者可查阅有关资料进行了解。

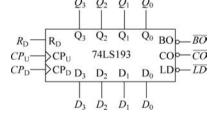

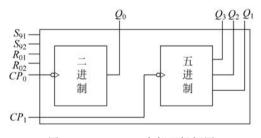

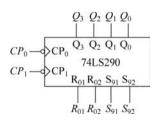

74LS290 是应用较广的一种集成异步二-五-十进制计数器,其内部逻辑框图如图 5-68 所示。它由两个独立的计数器构成,一个是 1 位二进制计数器,时钟脉冲为  $CP_0$ ,状态输出为  $Q_0$ ,另一个是异步五进制计数器,时钟脉冲为  $CP_1$ ,状态输出为  $Q_0Q_0$ .

74LS290 的简易图形符号如图 5-69 所示。其中, $R_{01}$ 、 $R_{02}$  为异步复位输入端, $S_{91}$ 、 $S_{92}$  为异步置 9 输入端。

图 5-68 74LS290 内部逻辑框图

图 5-69 74LS290 的简易图形符号

74LS290 有以下几种工作模式:

(1) 二进制计数器:以 CP。为计数脉冲输入端,Q。为计数输出端。

- (2) 五进制计数器:以 $CP_1$ 为计数脉冲输入端, $Q_2$ 、 $Q_2$ 、 $Q_1$ 为计数输出端。

- (3) 8421 码十进制计数器:以 $CP_0$ 为计数脉冲输入端, $CP_1$ 与 $Q_0$ 相连, $Q_2$ , $Q_3$ , $Q_4$ , $Q_5$ 为计数输出端。

- (4) 5421 码十进制计数器: 以  $CP_1$  为计数脉冲输入端, $CP_0$  与  $Q_0$  相连, $Q_0$ , $Q_0$ , $Q_0$ 为计数输出端。

74LS290 的功能表如表 5-35 所示。

| СР       | $R_{01} \cdot R_{02}$ | $S_{91} \cdot S_{92}$ | 工作状态 |

|----------|-----------------------|-----------------------|------|

| ×        | 1                     | 0                     | 复位   |

| ×        | 0                     | 1                     | 置 9  |

| <b>↓</b> | 0                     | 0                     | 计数   |

表 5-35 74LS290 的功能表

由表 5-35 可见,74LS290 具有以下功能:

- (1) 异步复位。当 $R_{01} \cdot R_{02} = 1, S_{91} \cdot S_{92} = 0$  时,74LS290 异步复位,即输出为 0000。

- (2) 异步置 9。当  $R_{01} \cdot R_{02} = \mathbf{0}, S_{91} \cdot S_{92} = \mathbf{1}$  时,74LS290 异步置 9,即输出为 **1001**。

- (3) 计数功能。当 $R_{01} \cdot R_{02} = \mathbf{0}, S_{91} \cdot S_{92} = \mathbf{0}$  时,74LS290 在计数脉冲下降沿作用下进行 计数。

#### 4. 集成计数器构成的任意进制计数器

由于常见的集成计数器一般都是二进制、十进制等几种类型,而不同场合可能需要其他类 型的计数器,例如电子钟上就需要十二进制、二十四进制、六十进制的计数器。若要构成其他 任意进制计数器,只能利用已有的计数器类型,并增加外电路构成。假定已有 N 进制计数器, 要得到M进制计数器,有以下两种可能情况。

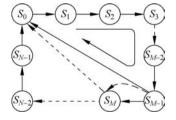

#### 1) M < N 的情况

当 M < N 时,需要设法让 N 进制计数器自动跳过 N - M 个状态,就可以得到所需的 M进制计数器。实现这种自动跳跃的方法有复位法和置数法两种。

#### (1) 复位法。

复位法适用于具有复位输入端的计数器。如果已有的 N 进制计数器具有异步复位输入 端,则采用复位法得到 M 进制计数器的方法是: N 进制计数器从全 0 的状态 S。开始计数并 接收了M个计数脉冲后,电路进入 $S_M$ 状态。如果将 $S_M$ 状态译码产生一个复位信号加到异

步复位输入端,则计数器将立即返回 S。状态。由于电路进入  $S_M$  状态后立即被置成  $S_0$  状态,使  $S_M$  状态仅在极短的瞬间出 现,所以在稳定的有效循环中不应包括  $S_M$  状态。这样就实现 了自动跳过 N-M 个状态而得到所需的 M 进制计数器。

如果已有的 N 进制计数器具有同步复位输入端,由于复位 信号到来后,必须要等到下一个时钟信号到达后才能将计数器 复位,这时要得到M进制计数器就必须将 $S_{M-1}$ 状态译码输出 复位信号,所以  $S_{M-1}$  状态应包含在 M 进制计数器的稳定状态 循环中。图 5-70 是复位法原理示意图。

图 5-70 复位法获得任意 进制的方法

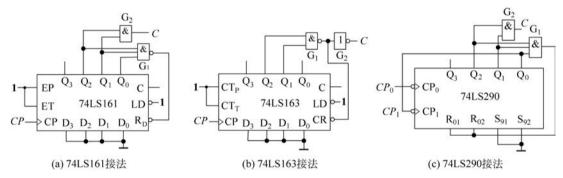

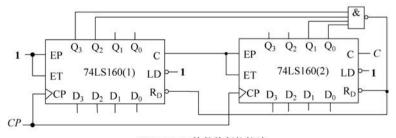

【例 5-15】 试采用复位法将 74LS161 和 74LS163 及 74LS290 分别接成七进制计数器。

解: 七进制计数器的有效循环状态为 0000→0001→···→0110→0000。74LS161 具有

异步复位输入端,需要洗取输出状态 0111 经译码产生复位信号加到 74LS161 的异步复位 输入端即可,如图 5-71(a)所示。将  $Q_{\circ}$ 、 $Q_{\circ}$ 、 $Q_{\circ}$ 接到"与非"门  $G_{\circ}$ 的输入端, $G_{\circ}$ 的输出端与 74LS161 的异步复位输入端 $\overline{R}_0$  相连。当 74LS161 进入状态  $Q_3Q_2Q_1Q_0=0111$  时, $G_1$  门输 出低电平,74LS161 异步复位。0111 状态仅在极短的瞬间出现,在稳定的有效循环中不包 括 0111 状态,也不能用此状态产生进位信号,故进位信号是从 0110 状态产生的。

74LS163 具有同步复位输入端,需要选取输出状态 0110 经译码产生复位信号加到 74LS163 的同步复位输入端即可,如图 5-71(b)所示。将  $Q_{2}$ ,  $Q_{1}$  接到"与非"门  $G_{1}$  的输入端,  $G_1$  的输出端与 74LS163 的同步复位输入端  $\overline{CR}$  相连。当 74LS163 进入状态  $Q_2Q_2Q_1Q_0=$ **0110** 时,"与非"门输出低电平,经  $G_2$  反相后产生进位信号 C。此时 74LS163 不会被立即复 位,必须在下一个时钟脉冲到来时才复位,故在稳定的有效循环中应包括 0110 状态。

74LS290 是异步二-五-十进制计数器,首先将其接成十进制形式,即将  $CP_1$  接  $Q_0$  端。 74LS290 具有高电平有效的异步复位输入端,需要选取输出状态 0111 经"与"门 G,译码产生 复位信号加到复位输入端即可,进位信号接法与 74LS161 相同,如图 5-71(c)所示。

图 5-71 用复位法实现七进制计数器

#### (2) 置数法。

置数法适用于具有预置数功能的计数器。置数法是通过给计数器重复置入某个数值 的方法跳过 N-M 个状态,从而获得 M 进制计数器。置数操作可以在电路的任一状态下 进行。具体方法是: 使 N 进制计数器从预置状态开始计数,在计满 M 个状态时,产生一个 置数控制信号加到预置数端进行置数,使计数器跳过 N-M 个状态获得 M 进制计数器。

图 5-72 置数法原理示意图

对于同步预置数计数器,若预置信号从S,状态译出, 必须要等到下一个 CP 信号到来时,才能将数据置入计数 器中,因此稳定循环中包含S,状态;对于异步预置数计数 器,只要预置信号一出现,立即将数据置入计数器中,不受 CP 信号的影响。因此,预置信号应从  $S_{i+1}$  状态译出。  $S_{i+1}$  状态只在极短的瞬间出现,稳定循环中不包含此状态。 图 5-72 是置数法原理示意图。

【例 5-16】 试采用置数法将 74LS160 接成七进制

## 计数器。

解:由于同步预置数计数器 74LS160 具有十个有效状态,采用置数法时,置数状态可从 这十个状态中任选,故实现七进制计数器的方法并不唯一。

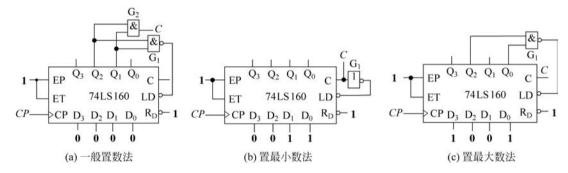

选择从 0000 状态开始,有效循环状态为  $0000 \rightarrow 0001 \rightarrow \cdots \rightarrow 0101 \rightarrow 0110$ ,将  $Q_{\circ}, Q_{\circ}$  接到

"与非"门 $G_1$ 的输入端, $G_1$ 的输出端与同步置数端相连。当计数器进入状态 **0110** 时, $G_1$ 输出低电平,在下一个时钟脉冲到来时才置入 **0000** 状态,从而跳过其他状态,并将  $Q_2$ 、 $Q_1$ 端接到"与"门 $G_2$ 产生进位信号 C,改接方法如图 5-73(a)所示。

上述方法有效循环不经过计数器的最后一个状态 **1001**,所以原计数器的进位输出 C 恒为 0。若利用原来计数器的进位输出信号作为新计数器的进位输出信号 C,可使改接电路更简单,图 5-73(b)、(c)给出了置最小数法和置最大数法的改接图。

用置最小数法时,有效状态为 0011~1001,当计数器状态达到 1001 时,置数端得到低电平信号,在下一个时钟脉冲到来时状态置为 0011。

用置最大数法时,有效状态为 0000~0101 和 1001,当计数器状态达到 0101 时,置数端得到低电平信号,在下一个时钟脉冲到来时状态置为 1001。

图 5-73 用置数法将 74LS160 接成七进制计数器

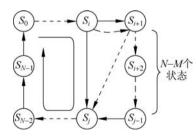

#### 2) M>N 的情况

当 M > N 时,必须将多片 N 进制计数器组合起来,才能形成 M 进制计数器。

如果 M 可分解成两个小于 N 的因数相乘,即  $M=N_1\times N_2$ ,则可采用串行进位方式或并行进位方式将一个  $N_1$  进制计数器和一个  $N_2$  进制计数器连接起来,构成 M 进制计数器。

串行进位方式连接是指低位计数器的进位信号连接到高位计数器的时钟端。

并行进位方式连接是指两个计数器的时钟同时接入计数脉冲,低位进位控制高位的计数 使能信号。

如果 M 不能分解成  $N_1$  和  $N_2$  的乘积,则要采用整体复位方式或整体置数方式构成 M 进制计数器。

整体复位(或置数)方式的原理与 M < N 时的复位(或置数)法类似,首先用已有的 N 进制计数器连接成一个大于 M 进制的计数器,然后再利用前面介绍的复位(或置数)法实现 M 进制计数器。

【注意】 整体复位方式和整体置数方式对于所有 M > N 的情况都适用。

【**例 5-17**】 试用两片 74LS160 实现一百进制计数器。

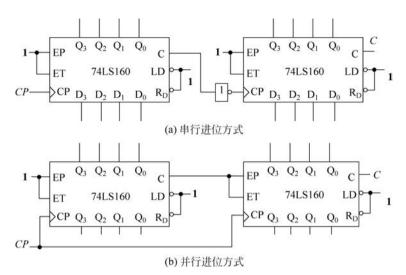

解:因为 100=10×10,因此用两片十进制计数器 74LS160 可以连成一百进制计数器。这里分别采用串行进位方式和并行进位方式来实现,如图 5-74(a)、(b)所示。

在图 5-74(a)中,两片 74LS160 的 EP 和 ET 端均接高电平,都工作在计数状态。当低位片计到 1001 时,输出端 C 变为高电平,经反相器后使高位片的 CP 端为低电平。下一个计数脉冲到达后,低位片计成 0000, C 跳回低电平,反相后有正跳变,使高位片计入 1。

在图 5-74(b)中,以低位片的输出 C 作为高位片 EP 和 ET 的输入,当低位片每计到 **1001** 时产生进位,使高位片处于计数工作状态,计入 **1**,低位片计成 **0000**。

图 5-74 例 5-17 逻辑电路图

【**例 5-18**】 分别用 74LS160 和 74LS161 构成六十进制计数器。

解: 构成六十进制计数器需用两片集成计数器,可采用整体置数或复位的方法,也可采用 分解的方法。这里采用整体置数和整体复位的方法来实现。

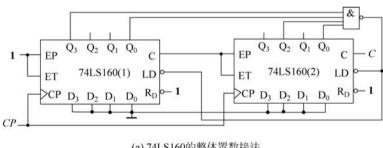

首先,将两片74LS160接成10×10=100进制计数器,将两片74LS161接成16×16=256 进制计数器,再将它们接成六十进制计数器。

74LS160 是十进制的计数器,进位规律是逢十进一,即按着8421 码规则计数,所以只要将 个位的 74LS160(1)接成 9(1001),将十位的 74LS160(2)接成 5(0101),然后采用整体置数法 使计数器形成 00~59 状态循环即可,每当状态到达 59 时,触发置数输入端有效,下一个时钟 脉冲到来时将状态置为 00,如图 5-75(a)所示。

(a) 74LS160的整体置数接法

(b) 74LS161的整体复位接法

图 5-75 例 5-18 的逻辑电路图

74LS161 是模 16 的 4 位二进制计数器,进位规律是逢十六进一,即按着自然 4 位二进制 数规则计数,所以需要将十进制数 60 变为 8 位二进制数,即 $(60)_{10}$  =  $(00111100)_{2}$ 。只要将个 位的 74LS161(1)接成 1100,将十位的 74LS161(2)接成 0011,然后采用整体复位法使计数器 形成 00000000~00111011 状态循环即可,每当状态到达 00111100(此状态非有效状态)时,触 发异步复位输入端有效,瞬间将状态置为"00000000",如图 5-75(b)所示。

#### \* 5.6 利用 Multisim 分析时序逻辑电路

#### 两位同步二进制计数器的仿真分析 5.6.1

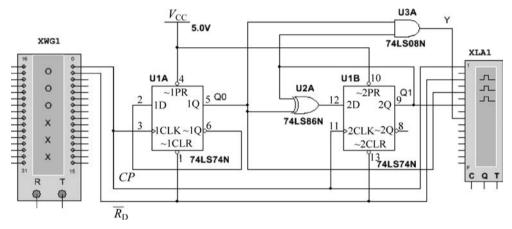

在 Multisim 13.0 中构建如图 5-76 所示的两位同步二进制加法计数器仿真电路。在元件 工具栏的 TTL 器件库中选出上升沿触发的 D 触发器 74LS74N、"与"门 74LS08N、"异或"门 74LS86N: 从电源/信号源库中选出电压源。同样也可以使用快捷键 Ctrl+W 调出选用元件 对话框,再找出相应的元件。从虚拟仪器工具栏中选出字信号发生器 XWG1、逻辑分析 仪 XLA1。

图 5-76 两位同步二进制计数器的仿真电路

双击字信号发生器的图标打开面板图,在字信号编辑区编辑时钟脉冲信号 CP 和直接复 位信号 $\bar{R}_{\rm D}$ , 若以十六进制(Hex)形式,则依次输入 0.2.3.3.2.2.3.3.2.2.3.3.2.2.3.3.2.2.2共 18 个字组数据。单击最后一个字组数据进行循环字组信号终止设置(set final position), 完成所有字组信号的设置;在 Frequency 区设置输出字信号的频率。

单击字信号发生器面板图 Control 区中的 Brust,电路开始仿真,字信号发生器从第一个 字组信号开始逐个字组输出直到终止字组信号。

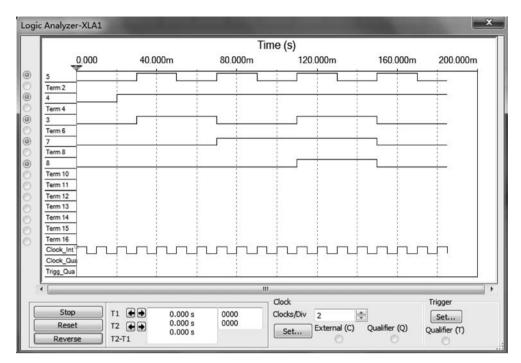

双击逻辑分析仪 XLA1 图标打开面板图,显示波形图如图 5-77 所示。在面板图的 Clock 选项区,通过 Clocks/Div 框设置每个水平刻度显示的时钟脉冲个数,要与字信号发生器输出 字信号的频率相互配合,使屏幕上显示一个计数周期的波形。

图 5-77 所示波形中,从上至下依次为计数时钟脉冲 CP、异步复位 信号  $R_0$ 、状态输出  $Q_0$ 和  $Q_1$ 、进位输出 Y。

由仿真结果可知, $\overline{R}_{D} = 0$ 时,各触发器初始状态均复位,计数器从 00状态开始计数。  $\bar{R}_{\rm D}=1$  期间,在时钟脉冲 CP 作用下完成从  $00\rightarrow 01\rightarrow 10\rightarrow 11$  共四个状态的循环变化,并产生 进位输出信号。故该计数器为两位同步二进制加法计数器。

图 5-77 两位同步二进制计数器的仿真波形

#### 用 74LS161N 构成六十进制计数器 5.6.2

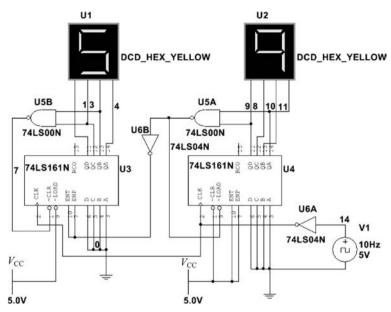

### 1. 并联进位方式

在 Multisim 13.0 中构建并联进位方式的六十进制计数器仿真电路,如图 5-78 所示。在 元件工具栏的 TTL 器件库中选出集成计数器 74LS161N、"与非"门 74LS00N、反相器 74LS04N: 从电源/信号源库中选出脉冲信号源、电压源及接地端,在指示元件库中选出共阴 极 LED 数码显示器,并在 Component 栏中选择颜色。也可以使用快捷键 Ctrl+W 调出选用 元件对话框,再找出相应的元件。

图 5-78 中反相器 U6A 的作用是将 74LS161N 的时钟脉冲触发方式修正为和实际器件— 致的上升沿触发。U4 集成计数器 74LS161N 采用置数法构成十进制计数器,U3 集成计数器 74LS161N 采用复位法构成六进制计数器,它们共用一个时钟脉冲信号,用 U5A 及 U6B 形成 的进位信号控制高位片 U3 的计数控制端 ENP 及 ENT 进行并联进位。

单击仿真开关,计数器开始计数,在计数时钟脉冲作用下从 00~59 进行六十个状态的循 环变化,实现并行进位方式的六十进制加法计数。

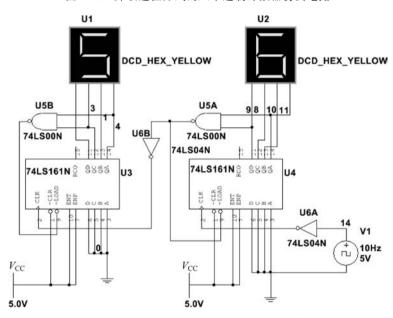

#### 2. 串联进位方式

在 Multisim 13.0 中构建串联进位方式的六十进制计数器仿真电路,如图 5-79 所示。图 中 U4 集成计数器 74LS161N 采用置数法构成十进制计数器, U3 集成计数器 74LS161N 也采 用置数法构成六进制计数器,用 U5A 形成的进位信号作为高位片 U3 的计数脉冲信号进行串 联进位。

单击仿真开关,计数器开始计数,在计数时钟脉冲作用下从 00~59 进行六十个状态的循 环变化,实现串联进位方式的六十进制加法计数。

图 5-78 并联进位方式的六十进制计数器仿真电路

图 5-79 串联进位方式的六十进制计数器仿真电路

#### \* 5.7 利用 VHDL 设计时序逻辑电路

本节用 VHDL 对十六进制计数器和移位寄存器进行设计和仿真。

## 1. 异步清零十六进制计数器的设计及仿真

设异步清零端为 clr,时钟输入端为 clk,输出端为 count。源代码为

```

library ieee;

use ieee. std_logic_1164.all;

use ieee. std_logic_unsigned.all;

```

```

entity counter16 is

port(clk,clr: in std logic;

count: out std_logic_vector(3 downto 0));

end counter16;

architecture beha of counter16 is

signal cnt: std logic vector(3 downto 0);

begin

process(clk,clr)

begin

if clr = '0'then

cnt <= "0000";

elsif clk = '1' and clk'event then

cnt < = cnt + '1';

end if;

count < = cnt;

end process;

end beha;

```

对源代码进行仿真,仿真结果如图 5-80 所示。

图 5-80 异步清零十六进制计数器的仿真图

### 2. 8 位移位寄存器的设计及仿真

设 d 为串行输入信号,clk 为时钟脉冲信号,b 为 8 位输出向量。源代码为

```

library ieee;

use ieee. std_logic_1164.all;

use ieee. std logic arith.all;

use ieee. std logic unsigned. all;

entity shift8 is

port(d,clk:in std_logic;

b: out std logic vector(7 downto 0));

end entity shift8;

architecture rtl of shift8 is

signal b_s : std_logic_vector(7 downto 0);

begin

process (clk)

begin

if rising_edge(clk) then

b s <= b s(6 downto 0) & d; -- 左移

-- 或者 b_s <= d & b_s(7 downto 1); -- 右移

end if;

b < = b s;

end process;

end rtl;

```

对源代码进行仿真,仿真结果如图 5-81 所示。

图 5-81 8 位移位寄存器的仿真图

# 本章小结

b[1] 80 b[0] 80

本章介绍了时序逻辑电路的相关知识,主要讲述了如下内容。

- (1) 时序电路的特点是当前时刻的输出不仅与当前时刻的输入有关,还与电路的原状态有关,因此时序电路是有记忆功能的逻辑电路,由组合电路和存储电路两部分组成,其中存储电路一般由若干个触发器构成。描述时序电路的逻辑功能有多种方法,包括逻辑表达式、状态转换表、状态表、状态转换图和时序图等。

- (2) 同步时序电路分析的关键是要求出电路的输出方程、驱动方程和状态方程,进而作出 状态转换表、状态转换图或时序图,依据这些描述方法来分析电路的逻辑功能。

- (3) 同步时序电路设计的关键是能正确建立原始状态表(图),并能通过化简获得最简状态表,再依据最简状态表进行状态编码,然后合理选择触发器类型,并根据编码后的状态转换表求出电路的驱动方程和输出方程,最终画出逻辑电路图,并检查电路是否能够自启动,如无法自启动,则需要修正设计。

- (4) 异步时序电路的分析与设计步骤,与同步时序电路的分析与设计步骤基本相同,但是 因为异步时序电路没有统一的时钟信号来控制所有存储电路的状态变化,因此,分析时应特别 注意状态变化与时钟的对应关系。

- (5) 寄存器分为数码寄存器和移位寄存器两种,移位寄存器又分为单向移位寄存器和双向移位寄存器。集成移位寄存器使用方便、功能全、输入和输出方式灵活。用移位寄存器不仅可以寄存数码,还可以实现数据的串行-并行转换、数据运算等功能。

- (6) 计数器是数字系统最常用的时序逻辑器件。计数器的基本功能是对输入时钟脉冲进行累加或累减计数,此外还可用于分频、定时、产生节拍脉冲、数字运算等。常用的集成计数器有二进制计数器、十进制计数器等,利用这些集成计数器可以实现任意进制的计数器。

# 习题

|    | 1. 填空题     |            |          |           |      |

|----|------------|------------|----------|-----------|------|

|    | (1) 时序电路由_ | 电路和        | 电路两部分组成。 | 描述时序逻辑电路的 | 的三组方 |

| 程分 | ·别是、_      | ·o         |          |           |      |

|    | (2) 时序电路按照 | 照其触发器是否有统一 | ·的时钟控制分为 | 时序电路和     |      |

| 序由 | 路。         |            |          |           |      |

# 198 ◀‖ 数字电路与逻辑设计(第3版・微课视频版)

|    | (3)  | 寄存器按照寄存功能      | 的不同可分为              | 寄存器和           | _寄存器。             |     |

|----|------|----------------|---------------------|----------------|-------------------|-----|

|    | (4)  | 某寄存器由D触发器      | 器构成,有四位代码           | 要存储,则此寄存器      | 必须有个              | 触   |

| 发器 |      |                |                     |                |                   |     |

|    | (5)  | 按计数进制的不同,可     | J将计数器分为             | 、和 <i>N</i> i  | 进制计数器等类型。         |     |

|    | (6)  | 按计数过程中数值的      | 的增减来分,可将计           | 数器分为、          | 、和                | _   |

| 三种 | 0    |                |                     |                |                   |     |

|    | 2. j | 选择题            |                     |                |                   |     |

|    | (1)  | 关于时序逻辑电路的      | 特点,下列叙述正确的          | 内是。            |                   |     |

|    |      | A. 电路任一时刻的轴    | <b>俞出只与当时输入信</b> 号  | 号有关            |                   |     |

|    |      | B. 电路任一时刻的箱    | <b>计出只与电路原来状态</b>   | 态有关            |                   |     |

|    |      | C. 电路任一时刻的箱    | 前出与输入信号和电路          | 各原来状态均有关       |                   |     |

|    |      | D. 电路任一时刻的辐    | <b>前出与输入信号和电</b> 路  | 洛原来状态均无关       |                   |     |

|    | (2)  | 摩尔型时序逻辑电路      | 的输出。                |                |                   |     |

|    |      | A. 仅与输入有关      |                     | B. 仅与电路现态有     | <b>ī</b> 关        |     |

|    |      | C. 与输入和电路现态    | 5均有关                | D. 与输入和电路现     | 见态均无关             |     |

|    | (3)  | N 个触发器可以构成     | 寄存位二进               | 制数码的寄存器。       |                   |     |

|    |      | A. $N-1$       | B. <i>N</i>         | C. $N+1$       | D. 2 <i>N</i>     |     |

|    | (4)  | N 个触发器可以构成     | 最大计数长度(进制等          | 数)为的计数         | 汝器 。              |     |

|    |      | A. <i>N</i>    | B. 2N               | C. $N^2$       | D. $2^N$          |     |

|    | (5)  | 4 位二进制加法计数器    | 器正常工作时,从000         | 0 状态开始计数,经过    | 过四十三个输入计数         | 脉   |

| 冲后 | ,计   | 数器的状态是         | _ •                 |                |                   |     |

|    |      | A. <b>0011</b> | В. 1011             | C. <b>1010</b> | D. <b>1101</b>    |     |

|    | (6)  | 可以用来实现并/串转     | 专换和串/并转换的器          | 件是。            |                   |     |

|    |      | A. 移位寄存器       | B. 全加器              | C. 译码器         | D. 计数器            |     |

|    | (7)  | 由两个模数分别为 M     | $I_1$ 和 $M_2$ 的计数器串 | 联而构成的计数器,其     | 其总模数为             | _ 0 |

|    |      | A. $M_1 + M_2$ | B. $M_1 \times M_2$ | C. $M_1 - M_2$ | D. $M_1 \div M_2$ |     |

|    | (8)  | 下列电路不属于时序      | 逻辑电路的是              | °              |                   |     |

|    |      | A. 数码寄存器       | B. 编码器              | C. 触发器         | D. 可逆计数器          |     |

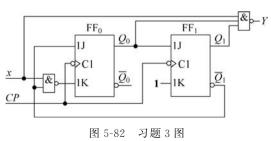

|    | 3. / | 分析如图 5-82 所示电员 | 路,写出它的驱动方和          | 星、状态方程和输出力     | 方程,列出状态表并         | 画   |

| 出状 | 态图   |                |                     |                |                   |     |

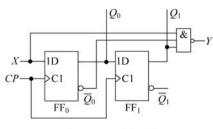

|    | 4.   | 分析如图 5-83 所示电影 | 路,写出它的驱动方和          | 星、状态方程和输出力     | 方程,列出状态表并         | 画   |

出状态图。

习题 4 图 图 5-83

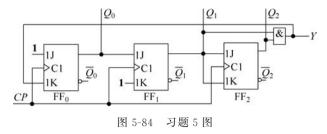

5. 试分析如图 5-84 所示时序电路逻辑功能,要求列出电路的驱动方程、输出方程、状态 方程,画出状态图。

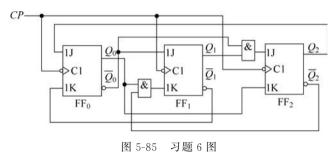

6. 试分析如图 5-85 所示时序电路逻辑功能,要求列出电路的驱动方程、输出方程、状态 方程,画出状态图。

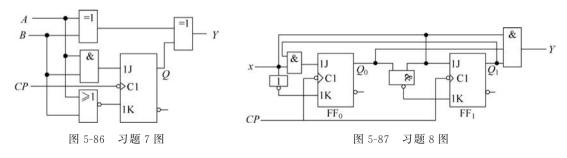

- 7. 试分析如图 5-86 所示同步时序电路逻辑功能,要求列出电路的驱动方程、输出方程、 状态方程,画出状态图。

- 8. 试分析如图 5-87 所示同步时序电路逻辑功能,要求列出电路的驱动方程、输出方程、 状态方程,画出状态图。

9. 图 5-88 所示电路是一个由计数器和 4 选 1 数据选择器构成的序列信号发生器,试分析 计数器的状态转换关系和模数,以及在计数器控制下数据选择器的输出序列(设计数器初始状 态为 000)。

图 5-88 习题 9 图

## 200 ◀ || 数字电路与逻辑设计(第3版・微课视频版)

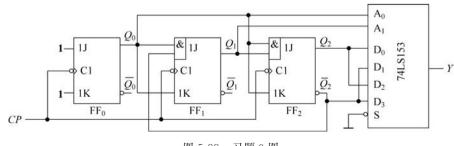

- 10. 试用维持-阻塞式 D 触发器和"与非"门设计一个同步时序电路,其状态图如图 5-89 所示。

- 11. 用"与非"门和 JK 触发器设计一个同步时序电路,以检测输入的信号序列是否为连续的 **101**。

- 12. 试用 JK 触发器和门电路设计一个同步六进制加法计数器。

- 13. 试用 D 触发器和门电路设计一个同步可控计数器, 当 M=0 时, 其状态迁移为

当M=1时,其状态迁移为

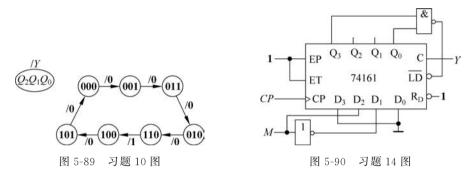

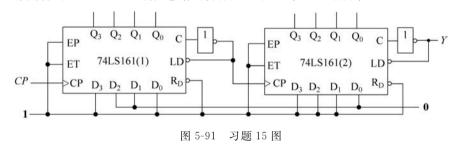

14. 试分析如图 5-90 所示计数器,在 M=0 和 M=1 时各为几进制计数器?

15. 试分析如图 5-91 所示计数电路的分频比(即 Y 与 CP 的频率之比)。

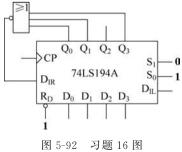

16. 试分析如图 5-92 所示时序电路的功能。

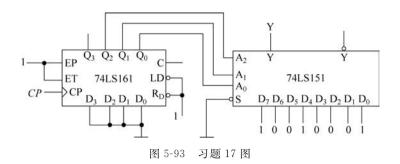

- 17. 如图 5-93 所示电路是由 74LS161 和 74LS151 构成的序列信号发生器,求输出序列信号。

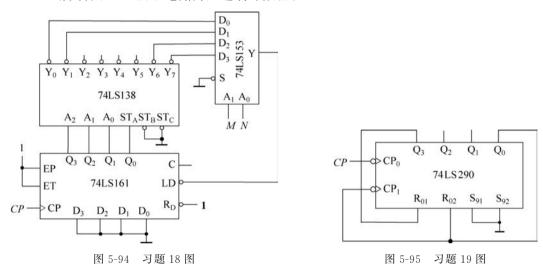

- 18. 图 5-94 所示电路是一个可变计数器,试确定 MN = 01 和 MN = 10 时,电路分别构成

## 几进制计数器?

19. 试分析图 5-95 所示电路为几进制计数器。

- 20. 分别用复位法和置数法将 74LS161、74LS163 接成十二进制计数器。

- 21. 分别用复位法和置数法将 74LS160 接成六进制计数器。